FPGA架构的功耗

[09-12 18:34:08] 来源:http://www.88dzw.com EDA/PLD 阅读:8323次

文章摘要: 减少FPGA的功耗可带来许多好处,如提高可靠性、降低冷却成本、简化电源和供电方式、延长便携系统的电池寿命等。无损于性能的低功耗设计既需要有高功率效率的FPGA架构,也需要有能驾驭架构组件的良好设计规范。本文将介绍FPGA的功耗、流行的低功耗功能件以及影响功耗的用户选择方案,并探讨近期的低功耗研究,以洞察高功率效率FPGA的未来趋势。功耗的组成部分FPGA的功耗由两部分组成:动态功耗和静态功耗。信号给电容性节点充电时产生动态功耗。这些电容性节点可以是内部逻辑块、互连架构中的布线导线、外部封装引脚或由芯片输出端驱动的板级迹线。FPGA的总动态功耗是所有电容性节点充电产生的组合功耗。静态功

FPGA架构的功耗,标签:eda技术,eda技术实用教程,http://www.88dzw.com减少FPGA的功耗可带来许多好处,如提高可靠性、降低冷却成本、简化电源和供电方式、延长便携系统的电池寿命等。无损于性能的低功耗设计既需要有高功率效率的FPGA架构,也需要有能驾驭架构组件的良好设计规范。

本文将介绍FPGA的功耗、流行的低功耗功能件以及影响功耗的用户选择方案,并探讨近期的低功耗研究,以洞察高功率效率FPGA的未来趋势。

功耗的组成部分

FPGA的功耗由两部分组成:动态功耗和静态功耗。信号给电容性节点充电时产生动态功耗。这些电容性节点可以是内部逻辑块、互连架构中的布线导线、外部封装引脚或由芯片输出端驱动的板级迹线。FPGA的总动态功耗是所有电容性节点充电产生的组合功耗。

静态功耗与电路活动无关,可以产生于晶体管漏电流,也可以产生于偏置电流。总静态功耗是各晶体管漏电功耗及FPGA中所有偏置电流之和。动态功耗取决于有源电容一侧,因而可随着晶体管尺寸的缩小而改善。然而,这却使静态功耗增加,因为较小的晶体管漏电流反而较大。因此静态功耗占集成电路总功耗的比例日益增大。

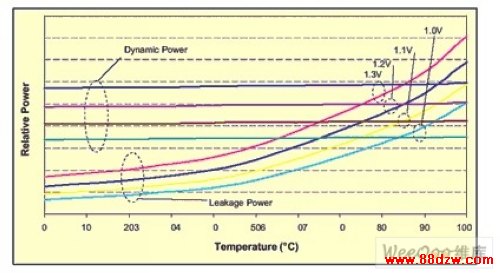

如图1所示,功耗很大程度上取决于电源电压和温度。降低FPGA电源电压可使动态功耗呈二次函数下降,漏电功耗呈指数下降。升高温度可导致漏电功耗呈指数上升。例如,把温度从85℃升高至100℃可使漏电功耗增加25%。

图1 电压和温度对功耗的影响

功耗分解

下面分析一下FPGA总功耗的分解情况,以便了解功耗的主要所在。FPGA功耗与设计有关,也就是说取决于器件系列、时钟频率、翻转率和资源利用率。

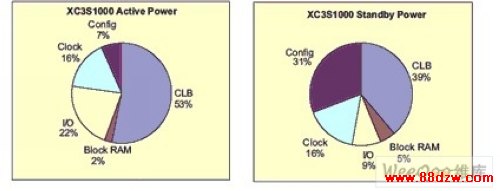

以Xilinx Spartan-3 XC3S1000 FPGA为例,假定时钟频率为100MHz,翻转率为12.5%,而资源利用率则取多种实际设计基准测试的典型值。

图2所示为XC3S1000的活动功耗和待机功耗分解图。据报告显示,活动功耗是设计在高温下活动时的功耗,包括动态和静态功耗两部分。待机功耗是设计空闲时的功耗,由额定温度下的静态功耗组成。CLB在活动功耗和待机功耗中占最主要部分,这不足为奇,但其他模块也产生可观的功耗。I/O和时钟电路占全部活动功耗的1/3,如果使用高功耗的I/O标准,其功耗还会更高。

图2 Spartan-3 XC3S1000 FPGA典型功耗分解图

配置电路和时钟电路占待机功耗近1/2,这在很大程度上是偏置电流所致。因此,要降低芯片的总功耗,就必须采取针对所有主要功耗器件的多种解决方案。

低功耗设计

FPGA的设计中使用了多种功耗驱动的设计技术。以Xilinx Virtex系列为例,因为配置存储单元可占到FPGA中晶体管数的1/3,所以在该系列中使用了一种低漏电流的“midox”晶体管来减少存储单元的漏电流。为了减少静态功耗,还全面采用了较长沟道和较高阈值的晶体管。动态功耗问题则用低电容电路和定制模块来解决。DSP模块中乘法器的功耗不到FPGA架构所构建乘法器的20%。鉴于制造偏差可导致漏电流分布范围很大,可筛选出低漏电流器件,以有效提供核心漏电功耗低于60%的器件。

除了融入FPGA设计之外,还有许多设计选择方案影响到FPGA的功耗。下面分析部分这类选择方案。

1 功耗估计

功耗估计是低功耗设计中的一个关键步骤。虽然确定FPGA功耗的最准确方法是硬件测量,但功耗估计有助于确认高功耗模块,可用于在设计阶段早期制定功耗预算。

如图1所示,某些外部因素对功耗具有呈指数的影响;环境的微小变化即可造成预估功耗的重大变化。使用功耗估计工具虽难以达到精准,但仍然可以通过确认高功耗模块来为功耗优化提供极好的指导。

《FPGA架构的功耗》相关文章

- › 高性能FPGA中的高速SERDES接口

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › FPGA在平板显示器中的应用

- › FPGA与DS18B20型温度传感器通信的实现

- 在百度中搜索相关文章:FPGA架构的功耗

- 在谷歌中搜索相关文章:FPGA架构的功耗

- 在soso中搜索相关文章:FPGA架构的功耗

- 在搜狗中搜索相关文章:FPGA架构的功耗

当前位置:

当前位置: