基于FPGA的模式可变的卫星数据存储器纠错系统

[09-12 18:34:23] 来源:http://www.88dzw.com EDA/PLD 阅读:8428次

文章摘要:采用(22,16)汉明码方案后,可以纠正每22比特内存行单元中的单比特错误。对于一行22比特编码记录,不发生SEU以及只有一比特发生SEU的概率和,即为该行内存单元的可靠性。因此,每22比特的行汉明码内存单元可靠性为:每22比特行单元的有效容量是16位,即2个字节。故对于有效大小为N字节的汉明码内存系统,由N/2个行单元构成。其可靠性为:而对于采用TMR的一行3比特的内存结构,可靠性为:对于一个有效大小为N字节的TMR内存系统,由8N个3比特结构组成,可靠性为:在实际航天应用中[3],通常10 -9>σ10 10bit-1・s -1。取N=4×10 6(即4兆字节),表1给出了σ取不同值

基于FPGA的模式可变的卫星数据存储器纠错系统,标签:eda技术,eda技术实用教程,http://www.88dzw.com

采用(22,16)汉明码方案后,可以纠正每22比特内存行单元中的单比特错误。对于一行22比特编码记录,不发生SEU以及只有一比特发生SEU的概率和,即为该行内存单元的可靠性。因此,每22比特的行汉明码内存单元可靠性为:

每22比特行单元的有效容量是16位,即2个字节。故对于有效大小为N字节的汉明码内存系统,由N/2个行单元构成。其可靠性为:

而对于采用TMR的一行3比特的内存结构,可靠性为:

对于一个有效大小为N字节的TMR内存系统,由8N个3比特结构组成,可靠性为:

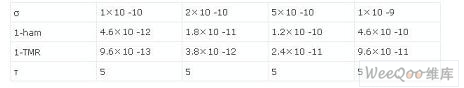

在实际航天应用中[3],通常10 -9>σ10 10bit-1・s -1。取N=4×10 6(即4兆字节),表1给出了σ取不同值时差错率(1-σ)的近似计算结果。其中差错率之经τ=(1-ρham)/(1-ρTMR)。

表1 实用参数下汉明码与TMR差率的近似比较

计算结果表明,在前述参数范围内,汉明码纠错的差错率约是TMR的5倍。而且,两种系统的差错率都与σ的平方近似成正比。可见即使采取内存纠错,设法降低σ仍是根据提高系统可靠性的主要措施。

系统的时序性能是考虑的另一个关键因素。尤其是在高达几十兆赫的内存总线上,编解码运算较为繁琐的汉明码方案有着相当的局限性。而TMR方案只需进行简单的2/3判决,通常更能胜任苛刻的内存访问时间要求。

2 可变方案配置

从上述比较可以看出,两种方案各有优势,适合在不同的环境条件和数据安全需求下应用。而星载计算机的通用性也要求数据存储器具有一定程度的灵活性。在综合上述两种方案的基础,结合目前飞速发展的现场可编程逻辑门阵列(FPGA)技术,提供了一种可以根据需要在线改变配置,分别实现上述两种EDAC方法的数据存储器方案。

2.1 可变内存配置

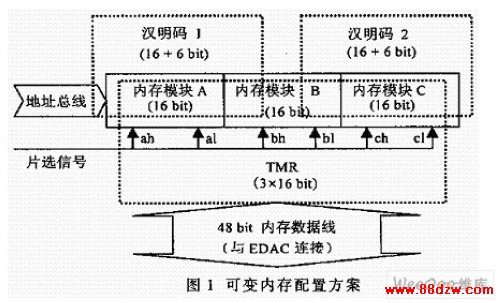

前述两种EDAC方法对于内存的配置是不同的。(22,16)汉明码一般采用16bit+8bit的内存芯片器件实现。而TMR则采用3×16bit的芯片实现。若要支持两种方法,必须为存储器设计一种特别的内存配置方式。这是模式可变的基础和关键。图1为可变内存配置方案。

这个数据存储系统是由3个位于同一条地址总线上的16bit内存模块组成。每个内存模块还可以单独片选其高字节或低字节。这样通过片选信号ah、al、bh、bl、ch、cl的控制,实际上有6个宽度为8bit的内存模块可以单独访问。48bit(3×16bit)的数据线全部接入EDAC控制模块。当系统工作在TMR模式时,ah、al、bh、bl、ch、cl被相同的片选信号驱动。这样就构成了TMR需要的一个3×16bit冗余内存空间。当系统工作在汉明码模式时,ah,al、bh一组,bl、ch、cl一组,分别被相同的片选信号驱动,构成了两个独立的16+8bit存储空间。对于(22,16)汉明码,每一个空间实际使用增加一倍。另外,系统还可以工作在无差错控制模式下。这时,ah、al一组,bh、bl一组,ch、cl一组,分别被相同的片选信号驱动,构成了三个独立的16bit存储空间。这种配置下的内存地址空间比TMR模式下增加两倍。在这些配置模式中,片选的地址译码都在EDAC控制模式中完成。

《基于FPGA的模式可变的卫星数据存储器纠错系统》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的模式可变的卫星数据存储器纠错系统

- 在谷歌中搜索相关文章:基于FPGA的模式可变的卫星数据存储器纠错系统

- 在soso中搜索相关文章:基于FPGA的模式可变的卫星数据存储器纠错系统

- 在搜狗中搜索相关文章:基于FPGA的模式可变的卫星数据存储器纠错系统

当前位置:

当前位置: