FPGA可重复配置和测试系统的实现

[09-12 18:34:28] 来源:http://www.88dzw.com EDA/PLD 阅读:8174次

文章摘要:图3 VC++6.0环境中断点调试指令发送图4 嵌入式逻辑分析仪SignalTAP II波形图4中ADS_N、BLAST_N、LWORD_N、LHOLD、LHOLDA是Local Bus的接口信号,ConfigEnd和ConfigStart是分别代表配置结束和配置开始的标志寄存器,LA是接口的地址信号,用于模块中控制寄存器的寻址,LD是接口的数据信号,用于指令数据的发送和数据的回收。以配置开始指令的发送为例,从图3图4两图中可以看出软硬件交互过程中的指令发送方式,在VC++中单步调试,发送一个开始指令0x01到配置命令寄存器地址0x01,通过硬件模块的接口动作,用嵌入式存储器SignalTap

FPGA可重复配置和测试系统的实现,标签:eda技术,eda技术实用教程,http://www.88dzw.com

图3 VC++6.0环境中断点调试指令发送

图4 嵌入式逻辑分析仪SignalTAP II波形

图4中ADS_N、BLAST_N、LWORD_N、LHOLD、LHOLDA是Local Bus的接口信号,ConfigEnd和ConfigStart是分别代表配置结束和配置开始的标志寄存器,LA是接口的地址信号,用于模块中控制寄存器的寻址,LD是接口的数据信号,用于指令数据的发送和数据的回收。

以配置开始指令的发送为例,从图3图4两图中可以看出软硬件交互过程中的指令发送方式,在VC++中单步调试,发送一个开始指令0x01到配置命令寄存器地址0x01,通过硬件模块的接口动作,用嵌入式存储器SignalTap II中捕捉到LA的数据为1h,LD上的数据为1h后ConfigStart寄存器置高,配置开始。

配置速度测试实验

软硬件具体方案设计完毕后,软件在Visual C++6.0环境下实现并调试。硬件在QuartusII7.1软件下编译。

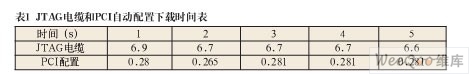

为了对比基于PCI总线的FPGA高速配置方案与基于ByteBlasterII JTAG下载电缆的速度性能,首先使用QuartusII7.1软件采用JTAG方式对FPGA2配置5次,计算每次下载所示时间,得到如表1中所示的数据;再使用本系统中基于PCI总线的配置功能对FPGA2配置5次,软件会自行计算总的下载时间,得到如表1中所示的数据:

从表1的数据对比中可以看到,基于PCI总线的自动下载配置方式要比基于JTAG电缆的下载配置方式提高超过20倍的速度,如果使用基于JTAG电缆对某大容量的FPGA下载需要近20分钟的话,使用PCI下载方式则只需不到1分钟的下载时间,具有明显的速度优势,大大节省了FPGA测试中的数据配置时间。

总结

该FPGA芯片测试平台具有以下特点:

(1)针对FPGA测试的特点:需要重复对待测FPGA配置,设计了FPGA在线配置模块和自动测试模块,从概念上初步实现了自动重复下载和重复测试的功能,为FPGA自动化测试寻找到一个好方法;

(2)利用软件的灵活性提高了测试系统中具有可观察性好和可控制性强的优势;利用硬件结构上并行度高、速度快的优势提高了测试的效率;

(3)相较于专业的ATE设备,该系统软件可控性更强,配置数据更方便。

- 上一篇:FPGA技术在视频处理领域的应用

《FPGA可重复配置和测试系统的实现》相关文章

- › 高性能FPGA中的高速SERDES接口

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › FPGA在平板显示器中的应用

- › FPGA与DS18B20型温度传感器通信的实现

- 在百度中搜索相关文章:FPGA可重复配置和测试系统的实现

- 在谷歌中搜索相关文章:FPGA可重复配置和测试系统的实现

- 在soso中搜索相关文章:FPGA可重复配置和测试系统的实现

- 在搜狗中搜索相关文章:FPGA可重复配置和测试系统的实现

当前位置:

当前位置: