采用FPGA实现 DisplayPort

[09-12 18:34:33] 来源:http://www.88dzw.com EDA/PLD 阅读:8678次

文章摘要:设计人员可使用支持赛灵思Platform. Studio (EDK) 的赛灵思嵌入式硬件设计套件或具有 SDK 的赛灵思嵌入式软件设计套件,对 XAPP 设计进行修改。通常情况下,FPGA 设计人员使用 EDK,而软件开发人员则使用SDK。EDK 流会生成一个中间网络文件 (NGC),您可以在实施设计之前,将其整合在项级 ISE 项目中。NGC文件包含构成 BRAM 初始化一部分的MicroBlaze 代码。如果用户修改过软件,EDK 流通常会占用较长的时间。不过,用户一旦生成了网络列表,就不再需要 EDK或者 SDK 了。SDK 流可修改 FPGA比特流,因此仅需更新 BRAM 中的Micr

采用FPGA实现 DisplayPort,标签:eda技术,eda技术实用教程,http://www.88dzw.com设计人员可使用支持赛灵思Platform. Studio (EDK) 的赛灵思嵌入式硬件设计套件或具有 SDK 的赛灵思嵌入式软件设计套件,对 XAPP 设计进行修改。通常情况下,FPGA 设计人员使用 EDK,而软件开发人员则使用SDK。

EDK 流会生成一个中间网络文件 (NGC),您可以在实施设计之前,将其整合在项级 ISE 项目中。NGC文件包含构成 BRAM 初始化一部分的MicroBlaze 代码。

如果用户修改过软件,EDK 流通常会占用较长的时间。不过,用户一旦生成了网络列表,就不再需要 EDK或者 SDK 了。SDK 流可修改 FPGA比特流,因此仅需更新 BRAM 中的MicroBlaze 代码内容。该 SDK 流能够为软件修改提供更快的转换时间,但在这种情况下,用户必须每生成一个比特流就使用一次 SDK。有关本专题的 XAPP 白皮书涵盖了如何使用赛灵思FPGA 嵌入式软件开发套件运行该设计的详尽说明。

该“入门指南”涵盖丰富信息,其中包括订购与许可、仿真、全系统硬件*估,以及技术支持等。此外,其还包含用户可用于生成范例设计的脚本文件,以及如何使用范例测试台与范例模式生成器进行仿真的说明。

用户可将该设计与从 TED Spartan-6FPGA 消费类视频套件中下载的完整版或*估版赛灵思DisplayPort LogiCORE以及 DisplayPort FPGA Mezzanine Card卡配合使用。

源端的 Policy Maker 内含一个状态机,可通过 AMBA?APB 端口或采用AMBA 至 PLB 桥的 32 位 PLBv46 总线连接至处理器接口。赛灵思在 BlockRAM 中存储了用户可修改的指令集。赛灵思用来调训 (train) 该链路的 C++代码不但是采用 GNU C++ 编译器编译的,并且还在采用赛灵思 EDK PlatformStudio 处理器设计套件的 FPGA 内部实施的软 MicroBlaze 处理器上进行了全面测试。参考设计包含完整的赛灵思 SDK项目。范例测试台可将一个 135MHz的时钟连接至 VID 时钟,并将一个100MHz 的时钟连接至 APB 时钟。赛灵思对所有输入是否连接正确进行检查。此外,顶级模块还提供复位功能。

扩展显示识别

DisplayPort 一个特别重要的特性是,能够通过 VESA 的增强显示识别2010年 夏季刊37手把手课堂:FPGA 101数据 (EDID) 结构与不同的设备进行接口相连。EDID 并不是什么新事物。实际上多年以来设计人员一直在使用各种视频接口读取 EDID 的宿端设备参数,从而与设备进行接口连接。不过这些早期的 EDID 及相关接口 技术通常不包含高级可配置通信通道。如今借助 DisplayPort,VESA 为系统增添了智能性,不但能在源端(如机顶盒、DVD 播放器或 PC 图形卡)与宿端设备(如显示.)之间进行功能协调,而且还可优化通信参数。DisplayPort v1.1a 可协调的变量包括通道数量(1、2 或者 4)、每信道数据速率(1.62 或 2.7Gbps)、电压摆幅(0.2、0.6、0.8、1.2 V)、4 个级别的通道预加重以及链路时钟向下扩散。

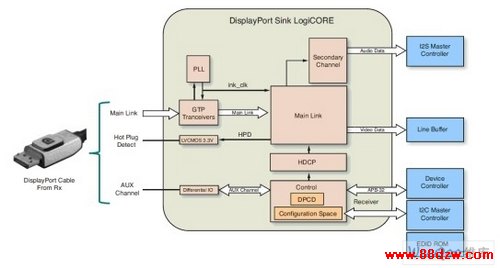

由 CORE Generator 生成,并与LogiCORE 一道提供的接收宿端范例设计可提供范例 EDID(见图 3),以便满足 EDID 源端设备的读取需求,确保用户的最佳视觉体验。

图3 DisplayPort 接收高级方框图

宿端范例设计在 FPGA 内部的BRAM 中实施了 EDID 数据结构。DisplayPort 的源代码可通过 AUX 通道实现 I2C 协议。图 3 和图 4 显示了连接至源端的 DisplayPort 宿端的方框图。宿端的 Link 与 Stream Policy Maker属于宿端内核的组成部分,不过源端的 LinkPolicy Maker 具有更高的复杂性,将作为源代码随参考设计提供。EDID 通过I2C 接口与接受宿端进行接口连接。

I2C 协议非常适合针对 EDID 数据结构的连接,并常常用于这种类型的应用。I2C 控制器负责定位与管理在EDID 中发现的数据,并通过串行接口与 I2C 接口协议(通过 AUX 通道)将数据传输至宿端内核。在工作模式下,用户无需知晓 EDID 是否正被访问。用户可通过检测 I2C 总线来监控 ROM 的内容。在调试模式下,用户能够修改I2C 控制器,覆盖 EDID ROM 提供的 3位内容。I2C 提供控制信号,在与适当的开集输出相连时,可提供 I2C 主接口。

《采用FPGA实现 DisplayPort》相关文章

- › 采用FPGA的红外密集度光电立靶测试系统

- › 采用FPGA实现 DisplayPort

- › 采用FPGA的可编程电压源系统原理及设计

- › 采用FPGA和DSP直接控制硬盘实现存储控制的方法

- › 采用FPGA实现100G光传送网

- › 采用FPGA实现发电机组频率测量计的设计

- 在百度中搜索相关文章:采用FPGA实现 DisplayPort

- 在谷歌中搜索相关文章:采用FPGA实现 DisplayPort

- 在soso中搜索相关文章:采用FPGA实现 DisplayPort

- 在搜狗中搜索相关文章:采用FPGA实现 DisplayPort

当前位置:

当前位置: