高速移动下OFDM均衡器的FPGA实现

[09-12 18:35:06] 来源:http://www.88dzw.com EDA/PLD 阅读:8500次

文章摘要:2.2.2 仿真结果实现该算法的重要一步是所设计的乘加器可以正常使用,并且实时性好。对其进行仿真如图6所示,可以发现当clk发生上升沿跳变时进行计算,图中信号(a,b)表示输入的数据信号;fcl表示相乘的结果;c表示进行乘加以后的运算结果,其计算准确,基本上没有延迟。ISE中设计的传输模块实现波特率为19 200 b/s的串口通信控制器,把数据通过RS 232完成FPGA与PC机的双向通信。把均衡后的信号Z(i)传回Matlab中,采用QPSK的星座图进行分析,选择子载波的数目N=128,循环前缀CP的长度为8,并且在认为信噪比被准确估计的情况下均衡的结果,如图7所示。由此星座图可以看出,在均

高速移动下OFDM均衡器的FPGA实现,标签:eda技术,eda技术实用教程,http://www.88dzw.com

2.2.2 仿真结果

实现该算法的重要一步是所设计的乘加器可以正常使用,并且实时性好。对其进行仿真如图6所示,可以发现当clk发生上升沿跳变时进行计算,图中信号(a,b)表示输入的数据信号;fcl表示相乘的结果;c表示进行乘加以后的运算结果,其计算准确,基本上没有延迟。

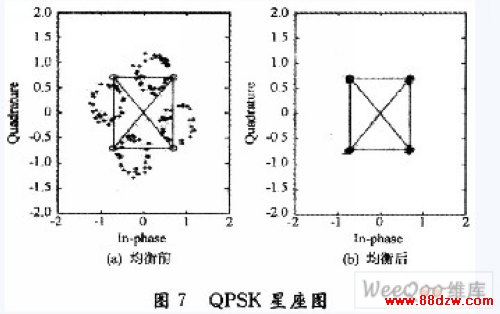

ISE中设计的传输模块实现波特率为19 200 b/s的串口通信控制器,把数据通过RS 232完成FPGA与PC机的双向通信。把均衡后的信号Z(i)传回Matlab中,采用QPSK的星座图进行分析,选择子载波的数目N=128,循环前缀CP的长度为8,并且在认为信噪比被准确估计的情况下均衡的结果,如图7所示。

由此星座图可以看出,在均衡前接收到的信号因为多普勒频移和噪声的影响,偏离星座点向周围发散,使用FPGA中均衡以后传回的数据基本没有发散现象。

3 结语

在ISE软件平台上使用Verilog语言实现了一种基于时变OFDM系统的低复杂度MMSE均衡器算法。在Xilinx公司Virtex-2实验板(XC2V930芯片)上对其进行验证,基本达到该算法在Matlab上仿真的均衡效果。但是由于浮点数计算量太大,选用定点数对其进行截取,还是有一定的局限性,在进行大量数据的运算中还是会有些数据不太准确,造成整体的误码率效果不是太好,故还需要进一步改进算法和FPGA的实现方法,以期达到更好的均衡效果。

Tag:EDA/PLD,eda技术,eda技术实用教程,EDA/PLD

《高速移动下OFDM均衡器的FPGA实现》相关文章

- › 高速移动下OFDM均衡器的FPGA实现

- 在百度中搜索相关文章:高速移动下OFDM均衡器的FPGA实现

- 在谷歌中搜索相关文章:高速移动下OFDM均衡器的FPGA实现

- 在soso中搜索相关文章:高速移动下OFDM均衡器的FPGA实现

- 在搜狗中搜索相关文章:高速移动下OFDM均衡器的FPGA实现

分类导航

最新更新

当前位置:

当前位置: