基于FPGA的快速9/7整形离散小波变换系统设计

[09-12 18:35:18] 来源:http://www.88dzw.com EDA/PLD 阅读:8156次

文章摘要: 摘要:CCSDS图像数据压缩标准中采用9/7整形离散小波变换为核心算法,该算法结构简单,易于硬件设计实现。文中基于FPGA设计实现了9/7整数离散小波变换系统,设计中使用内部RAM存储方式,减小了对存储器的需求量,同时采用基于行的列变换方式,行、列变换同时进行,提高了运行速度,仿真和综合结果显示该设计需要的硬件资源少,运行速度快。美国空间数据系统咨询委员会(简称CCSDS)于2005年推出一套适用于空间领域的图像压缩标准,标准使用了离散小波变换为核心算法,推荐使用9/7整数离散小波变换实现无损图像压缩,由于该算法结构简单,易于硬件设计实现,因此可以用FPGA来实现提升小波算法。1 C

基于FPGA的快速9/7整形离散小波变换系统设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com摘要:CCSDS图像数据压缩标准中采用9/7整形离散小波变换为核心算法,该算法结构简单,易于硬件设计实现。文中基于FPGA设计实现了9/7整数离散小波变换系统,设计中使用内部RAM存储方式,减小了对存储器的需求量,同时采用基于行的列变换方式,行、列变换同时进行,提高了运行速度,仿真和综合结果显示该设计需要的硬件资源少,运行速度快。

美国空间数据系统咨询委员会(简称CCSDS)于2005年推出一套适用于空间领域的图像压缩标准,标准使用了离散小波变换为核心算法,推荐使用9/7整数离散小波变换实现无损图像压缩,由于该算法结构简单,易于硬件设计实现,因此可以用FPGA来实现提升小波算法。

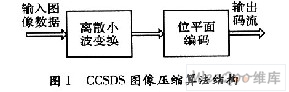

1 CCSDS图像压缩标准中的小波变换

CCSDS图像压缩算法主要包括两个功能模块:前一部分是对遥感图像数据进行离散小波变换,去除图像数据之间的冗余;后一部分是对去相关后的图像数据进行位平面压缩编码,如图1所示。

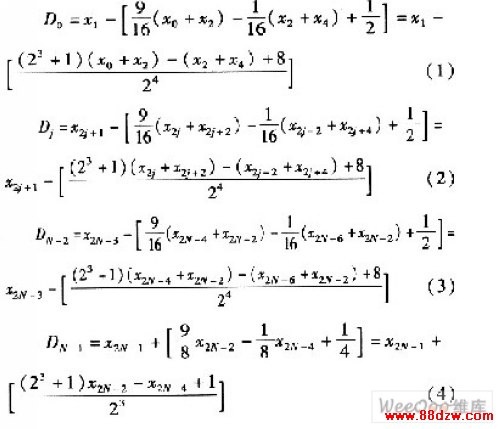

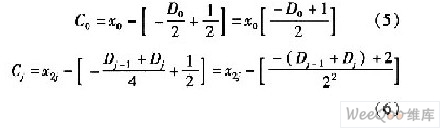

CCSDS标准推荐使用9/7离散小波滤波器对图像数据进行变换,即滤波器的低通系数为9个,滤波器的高通系数为7个。对于长度为2N待变换图像的原始数据Xk(k=0,1,2,…,2N-1),其整形小波变换公式如式(1)~式(6)所示。

其中,[]为对数据进行下取整操作;Cj为低通小波系数输出;Dj为高通小波系数输出。为了避免乘法器运算的繁琐,对公式进行了变形,采用加法器和移位操作实现公式的运算,提高了运算速度。

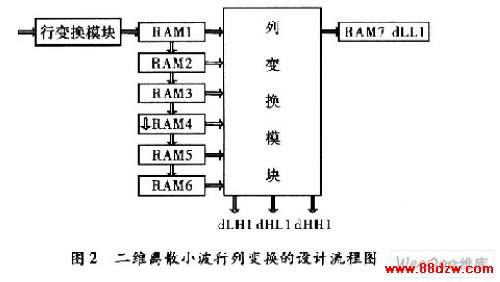

2 9/7二维离散小波变换的系统设计过程

本文在Xilinx公司提供的ISE7.1集成设计软件环境下,采用VHDL语言设计实现9/7二维离散小波变换系统,首先进行小波行变换,行变换后的数据按照行数输入内部RAM缓存,然后对行变换后的数据再进行列变换,最后将低频系数dLLl输入RAM缓存,其余高频系数dLHl,dHLl,dHHl输出到外挂RAM中缓存,系统设计流程,如图2所示。

2.1 行变换过程

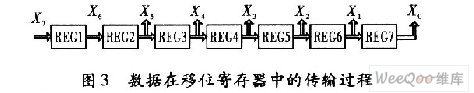

首先,使用7个移位寄存器来实现对数据的读写传输,每到来一个时钟控制信号(clk),就往移位寄存器中读写一个数据,数据在移位寄存器中的传输过程,如图3所示。

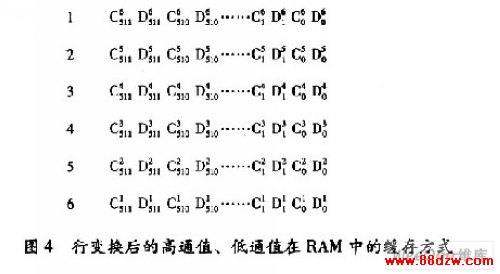

当输入第5个数据时,就可以根据式(1)和式(5)分别计算出第一个高通系数值D0和第一个低通系数值C0,下一个时钟控制信号读入第6个数据时,不进行操作,当控制读入第7个数据时,根据式(2)和式(6)分别计算出第2个高通系数值Dj和第2个低通系数值Cj,小波行变换后的高通系数D和低通系数C采用地址传输的方式交叉存储到6个内部RAM当中,如图4所示。

- 上一篇:基于FPGA的UART设计与实现

《基于FPGA的快速9/7整形离散小波变换系统设计》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的快速9/7整形离散小波变换系统设计

- 在谷歌中搜索相关文章:基于FPGA的快速9/7整形离散小波变换系统设计

- 在soso中搜索相关文章:基于FPGA的快速9/7整形离散小波变换系统设计

- 在搜狗中搜索相关文章:基于FPGA的快速9/7整形离散小波变换系统设计

当前位置:

当前位置: