基于FPGA的图像调焦系统研究

[09-12 18:35:27] 来源:http://www.88dzw.com EDA/PLD 阅读:8820次

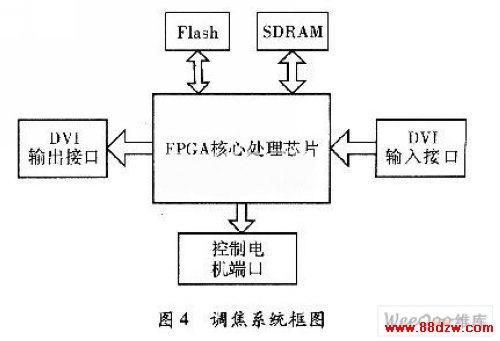

文章摘要:2 系统框图基于FPGA的自动调焦系统框图,如图4所示。其中图像的预处理过程,清晰度*价函数的算法实现过程,以及控制电机的算法实现和调焦过程都在FPGA中实现,并且进行实时处理。该模块共包含了5个模块3个部分,3个部分分别是输入端、处理过程和输出端。在处理过程中增加了SDRM与。Flash芯片。输入输出采用DVI接口,它们分别为TFP401输入DVI芯片和TFP410输出DVI芯片。FPGA核心处理芯片选用CyclONe3EP3-C5F256C8N芯片,其中包含10万个逻辑门,同时给图像数据提供缓冲使用2片IS4232400。由式(4)可知,对于一幅640×480的灰度图像,需要经过1 228

基于FPGA的图像调焦系统研究,标签:eda技术,eda技术实用教程,http://www.88dzw.com

2 系统框图

基于FPGA的自动调焦系统框图,如图4所示。其中图像的预处理过程,清晰度*价函数的算法实现过程,以及控制电机的算法实现和调焦过程都在FPGA中实现,并且进行实时处理。该模块共包含了5个模块3个部分,3个部分分别是输入端、处理过程和输出端。在处理过程中增加了SDRM与。Flash芯片。输入输出采用DVI接口,它们分别为TFP401输入DVI芯片和TFP410输出DVI芯片。FPGA核心处理芯片选用CyclONe3EP3-C5F256C8N芯片,其中包含10万个逻辑门,同时给图像数据提供缓冲使用2片IS4232400。

由式(4)可知,对于一幅640×480的灰度图像,需要经过1 228 800次乘法运算,307 200次开方运算,* 400次加法运算。由于计算量特别大,而且每一幅图像的变化不大,所以本系统采取了将图像划分为128×64大小的5个模块,首先对28×64大小的灰度图像进行傅里叶变换,然后获得图像的功率谱,再对其信号值进行加权,得到一块图像的清晰度*价值代替整个图像的清晰度*价值。同时采用“乒乓”操作,双蝶型处理器复用,基2FFT算法的FPGA实现方案。

3 调焦效果分析

对于清晰度*价算法和基于2-FFT的乘法实现结构的分析,得到这个图像的清晰度*价算法的乘法计算次数为(53 248×3+64×32×3)=165 888次,所需的加法计算次数为(53 248×3+64×32×2-1)=163 839次。由这些数据可知调焦过程中系统延时主要是这两个方面计算的延时相加,同时有电路系统的延时,但是这个延时在设计电路时已经考虑,限制在最小范围内,采用“乒乓”操作延时再加大约O.000ls的延时。当系统主频率为60 MHz时,经过实际的测试系统总延时大约为O.05s,实时处理的系统8帧图像的采集时间间隔要求为×0.04=0.32s。

满足实时性要求,上述系统的调试在Cyclone3EP3C5F256C8N芯片中实现,效果比较满意。

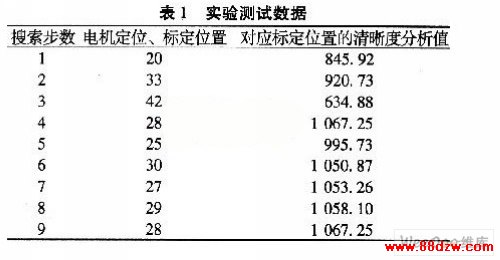

将镜头的焦距调节范围设置为60段,聚焦段的取值范围为[1,60]。测试时将一组由焦距从最远端开始发送过来的图像经过处理,搜索步数K,得到每次应该调焦的定位以及图像清晰度*价值,如表1所示。定位处为图像调焦效果最清晰处。

4 结束语

基于本模块的输入端口直接输入DVI信号,并非直接的采集图像端口,在实际应用中需要完成整个调焦过程,增加控制电机的控制电路模块,并对整个调焦过程的实时性进行综合*价。另外,基于图像技术的自动调焦方法有一个非常重要的应用前景是与CMOS图像传感器集成。由于CMOS图像传感器与FPGA采用了相同的制造工艺,所以是可以集成的。CMOS图像传感器集成了自动调焦功能后,不仅可以简化成像系统中自动调焦部分的设计,还提高了其与CCD图像传感器的竞争力。

《基于FPGA的图像调焦系统研究》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的图像调焦系统研究

- 在谷歌中搜索相关文章:基于FPGA的图像调焦系统研究

- 在soso中搜索相关文章:基于FPGA的图像调焦系统研究

- 在搜狗中搜索相关文章:基于FPGA的图像调焦系统研究

当前位置:

当前位置: