基于FPGA的宽带数字接收机变带宽数字下变频器设计

[09-12 18:35:32] 来源:http://www.88dzw.com EDA/PLD 阅读:8158次

文章摘要:MATLAB产生266阶原型低通滤波器系数,通过参数配置模块在DDC开始工作前存入RAM中,在参数配置模块中有专门的RAM写操作控制逻辑。由于抽取因子可在1~7之间灵活配置,则滤波器总的阶数可在138~738,即38~266之间变化,所以RAM中预存的滤波器系数应根据滤波器实际阶数灵活配置,多余的RAM存储空间置零。4 时钟重配置模块由于FPGA中的多个模块分别工作在不同的时钟频率,当DDC处理带宽变化时,系统输出数据率便发生变化,因而各模块的输入时钟频率也要发生变化。为了实现各模块输入时钟的动态配置,本设计使用了Altera的IP核 PLL的重配置功能(PLL Reconfiguration

基于FPGA的宽带数字接收机变带宽数字下变频器设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com

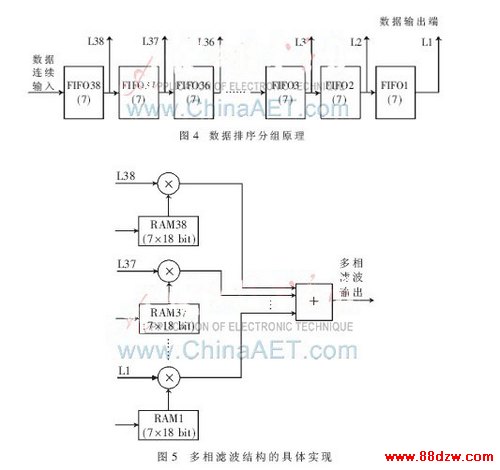

MATLAB产生266阶原型低通滤波器系数,通过参数配置模块在DDC开始工作前存入RAM中,在参数配置模块中有专门的RAM写操作控制逻辑。由于抽取因子可在1~7之间灵活配置,则滤波器总的阶数可在138~738,即38~266之间变化,所以RAM中预存的滤波器系数应根据滤波器实际阶数灵活配置,多余的RAM存储空间置零。

4 时钟重配置模块

由于FPGA中的多个模块分别工作在不同的时钟频率,当DDC处理带宽变化时,系统输出数据率便发生变化,因而各模块的输入时钟频率也要发生变化。为了实现各模块输入时钟的动态配置,本设计使用了Altera的IP核 PLL的重配置功能(PLL Reconfiguration),并且使用了Altera提供的专门用于PLL重配置的IP核(ALTPLL_RECONFIG),这样大大降低了整个系统时钟设计的难度,提高了DDC的灵活性。

5 系统总体调试

将以上各个模块按照图2所示的关系组合在一起,构成FPGA顶层文件。本设计充分利用了EP2S60F672C4上丰富的乘法器资源,使设计的VB-DDC性能达到了最佳。

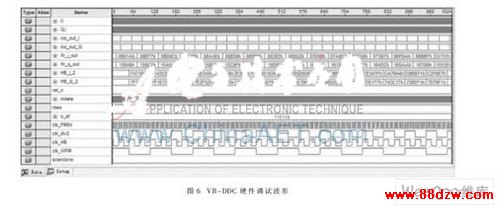

在SignalTap II中对整个VB-DDC系统进行调试的波形如图6所示。调试时,先在Altera提供的IP核 ROM中存入MATLAB仿真产生的14 bit LFM信号数据,信号带宽80 kHz,中频为32.4 MHz,以此模拟AD*5采样得到的数字中频信号。

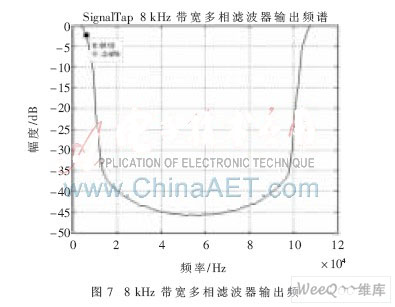

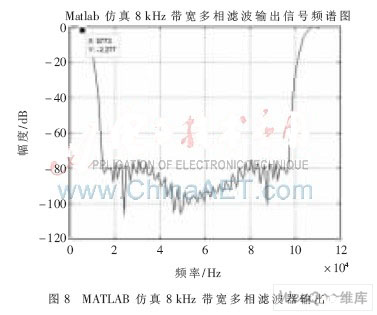

将VB-DDC配置成8 kHz带宽的基于多相滤波的266阶滤波器并级联在64阶FIR滤波器之后,将多相滤波器硬件调试输出 I_out_F、Q_out_F导入MATLAB进行频域分析如图7所示,其与图8的MATLAB理论仿真结果对比,可得设计满足要求。

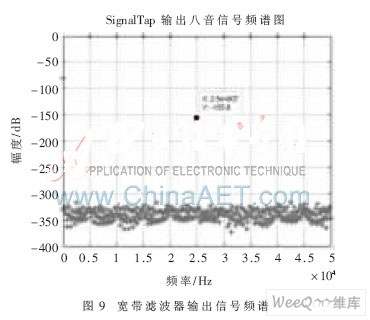

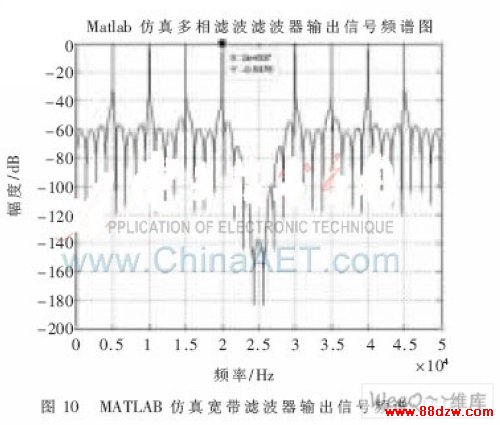

将采样率100 MHz、带宽40 MHz的八音信号输入VB-DDC系统。VB-DDC配置成宽带多相滤波器滤波,将硬件调试输出I_out_F、Q_out_F导入MATLAB进行频域分析如图9所示,其与图10的MATLAB理论仿真结果对比,可得设计满足要求。

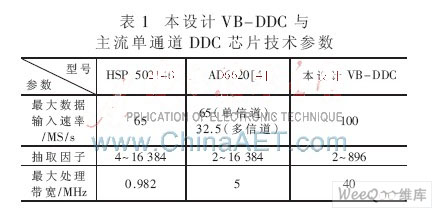

本文基于FPGA芯片Stratix II EP2S60F672C4设计了一个适用于宽带数字接收机的VB-DDC。该VB-DDC可根据处理信号带宽要求,灵活选择下变频器结构为传统结构的窄带DDC或者基于多相滤波结构的宽带DDC,也可以联合使用两种结构。表1列出了本设计VB-DDC与Intersil公司、ADI公司的两种单通道DDC芯片产品的主要技术参数,其中HSP50214B为目前各种单通道DDC产品*能最强的型号。本设计的VB-DDC在最大数据输入率和最大处理带宽这两项最重要的性能指标上占有很大优势。本设计的VB-DDC已经应用于宽带数字接收机系统。

《基于FPGA的宽带数字接收机变带宽数字下变频器设计》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的宽带数字接收机变带宽数字下变频器设计

- 在谷歌中搜索相关文章:基于FPGA的宽带数字接收机变带宽数字下变频器设计

- 在soso中搜索相关文章:基于FPGA的宽带数字接收机变带宽数字下变频器设计

- 在搜狗中搜索相关文章:基于FPGA的宽带数字接收机变带宽数字下变频器设计

当前位置:

当前位置: