基于FPGA的信道化接收机

[09-12 18:35:42] 来源:http://www.88dzw.com EDA/PLD 阅读:8913次

文章摘要:FPGA配置器件选择的是EPC16,采用同步并行配置方式(FPP)加载FPGA,用JTAG的方式可以给级联的3片FPGA依次加载程序,也可以给EPC-I6加载程序。3 FPGA内部信道化模块实现基于多相滤波的信道化模块是本系统的重点。根据文献,多相滤波信道化结构如图3所示。图3中分支上的信号xk(n)与输入信号x(n),以及分支滤波器Ek(n)与原型低通滤波器h0(n)之间的关系为:xk(n)=x(nD-k),Ek(n)=h0(nD+k)k=0,1,…,D-1。所以,进入分支上的数据与分支滤波器系数各是输入信号和原型低通滤波器系数的延时抽取得来。分支滤波器的长度定义为多相因子,本系统的多相因子

基于FPGA的信道化接收机,标签:eda技术,eda技术实用教程,http://www.88dzw.comFPGA配置器件选择的是EPC16,采用同步并行配置方式(FPP)加载FPGA,用JTAG的方式可以给级联的3片FPGA依次加载程序,也可以给EPC-I6加载程序。

3 FPGA内部信道化模块实现

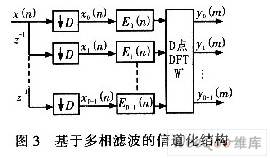

基于多相滤波的信道化模块是本系统的重点。根据文献,多相滤波信道化结构如图3所示。

图3中分支上的信号xk(n)与输入信号x(n),以及分支滤波器Ek(n)与原型低通滤波器h0(n)之间的关系为:xk(n)=x(nD-k),Ek(n)=h0(nD+k)k=0,1,…,D-1。所以,进入分支上的数据与分支滤波器系数各是输入信号和原型低通滤波器系数的延时抽取得来。分支滤波器的长度定义为多相因子,本系统的多相因子为8。

多相滤波的原型低通滤波器由MATLAB产生,采用函数REMEZ优化FIR滤波器估计算法,这里设计出来的滤波器通带截止频率为12.5 kHz,过渡带宽为11 kHz,阻带衰减为一100 dB。阶数为16 383阶。

图3所示的基于多相滤波器组的高效信道化结构,具有以下几个优点:1)各个支路共用一个低通FIR滤波器,减小FPGA用于存储系数的RAM资源;2)DFT可以用快速傅里叶变换FFT实现,提高计算效率;3)由于采用多相滤波结构,计算量上极大地减少,可实现性增强。这些优点为信道化结构的工程实现提供很好途径。

4 测试结果

系统输入测试信号为单频正弦信号,VPP为1 V,信号经过AD采样,DDC,信道化后,数据结果经过PCI上传给PC机作分析和显示。

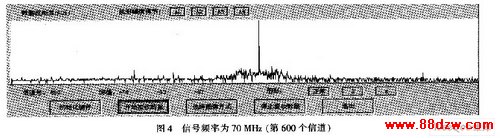

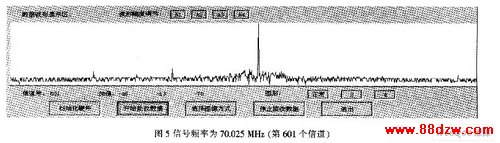

用Microsoft Visual C++6.0制作的界面中:横坐标是信道号,纵坐标是归一化功率值(dB),以数据形式显示的内容有:信号功率最大值对应的信道号、子信道输出相对于输入幅度的dB值以及相邻的两个信道的dB值。如图4和图5所示,输入信号频率分别为70 MHz,70.025 MHz,经过信道化后,在对应的信道号上都能输出谱线,频率分辨率达到25 kHz。经过多次重复测试,系统对相邻信道的带外抑制都达到55 dB以上。

5 结论

该系统主要器件包括AD*5、EP2S60,其中AD6*实现ADC,EP2S60负责系统控制、通信、算法实现,最终来实现了信道化接收功能。因此,该系统具有高度的灵活性和很强的通用性,可通过软件的重载或升级完成不同指标要求、不同模式的系统结构。在多板连接时,可以构成一个更大的阵列系统,可以用于DOA和DBF。

《基于FPGA的信道化接收机》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的信道化接收机

- 在谷歌中搜索相关文章:基于FPGA的信道化接收机

- 在soso中搜索相关文章:基于FPGA的信道化接收机

- 在搜狗中搜索相关文章:基于FPGA的信道化接收机

当前位置:

当前位置: