USB设备控制器端点缓冲区的优化技术设计

[09-13 16:54:52] 来源:http://www.88dzw.com 接口定义 阅读:8680次

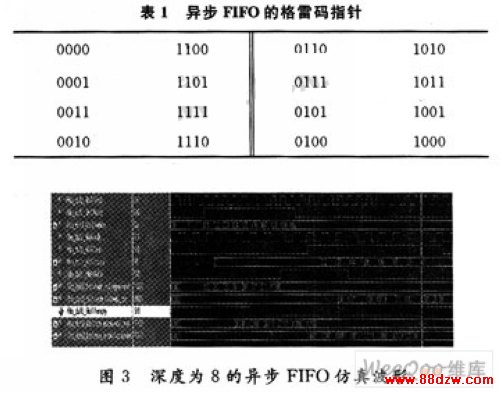

文章摘要:观察表1可知,当读指针为4’b0011时(二进制为4’b0010),此时比他多一个周期所对应的格雷码为4’b1111(二进制为4’b1010)。两者的高二位恰好相反,但低位完全相同。对比表1左右两列可知当读写指针相差一个周期即FIFO满时对应的格雷码指针的最高两位相反,而低位则完全相同;当两者完全相等时对应为FIFO的空状态。图3给出的是在设计的FIFO的深度为8时,在Modelsim中的仿真波形。由图3可知,当FIFO从空到满时,对应的格雷码写指针为4’b1100,而同步后的读指针为4’b0000;当从满被读空时,读指针为4’b1100;由此可见仿真的FIFO的空满信号与设计一致。2 基于F

USB设备控制器端点缓冲区的优化技术设计,标签:接口技术,微机原理与接口技术,http://www.88dzw.com

观察表1可知,当读指针为4’b0011时(二进制为4’b0010),此时比他多一个周期所对应的格雷码为4’b1111(二进制为4’b1010)。两者的高二位恰好相反,但低位完全相同。对比表1左右两列可知当读写指针相差一个周期即FIFO满时对应的格雷码指针的最高两位相反,而低位则完全相同;当两者完全相等时对应为FIFO的空状态。图3给出的是在设计的FIFO的深度为8时,在Modelsim中的仿真波形。由图3可知,当FIFO从空到满时,对应的格雷码写指针为4’b1100,而同步后的读指针为4’b0000;当从满被读空时,读指针为4’b1100;由此可见仿真的FIFO的空满信号与设计一致。

2 基于FIFO结构的优化端点设计方案

2.1 基于新型FIFO结构设计控制端点

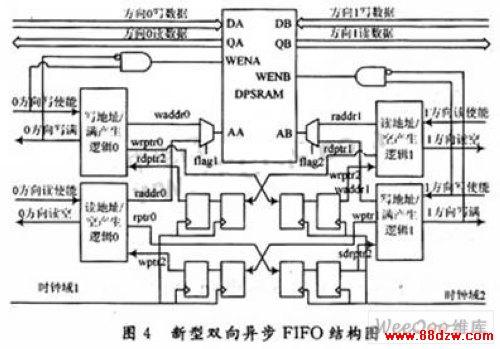

上文已经论述过控制端点是一个双向传输的端点,但是在同一时刻只能是单向的数据传输。该端点主要是用于USB设备的枚举过程,主机发送一个信息包,设备负责回应一个信息包。对于该端点的设计现有的方案都是采用双FIFO来实现双向传输的。一个FIFO用以接收主机发送过来的数据包;另外一个FIFO用以向主机发送数据包。在传输数据包时总有一个FIFO处于空闲状态,这样会造成存储器资源的浪费。为此,本文提出一种新型的异步FIFO结构,该结构使用一块双端口sram来实现控制端点的单工双向传输,而传统的双FIFO结构需要两块SRAM用来实现双向传输。由于SRAM占据了FIFO的大部分面积,在实现控制传输的功能下少用了一块SRAM,可以预见最终的电路实现面积会减小将近1/2。

图4是本文所设计的新型异步FIFO结构,该FIFO的实现是基于一块双端SRAM。在上文所提到的异步FIFO结构的基础上增加一套读写指针逻辑和满空判断标志。这个电路可以看作是原来电路模块的复制,即两者设计完全一致。这两个新增的指针模块用以产生访问SRAM的地址和用以产生满和空的格雷码指针。这样在同一方向对于SRAM的访问就会有两个地址,其中一个是读地址,另一个是写地址。这样需要设计一个选择器,用以选择当前访问SRAM的是读地址或写地址。这个选择器的选择端可以根据不同方向的读写使能信号来切换。这是由于在同一时刻不可能出现一个方向的读/写使能均有效的现象。

对于图4的数据路径可简介如下,方向0在其写使能信号的控制下,往FIFO内写入数据,写满之后方向1控制其读使能将方向0写入的数据读出来。然后方向1控制其写使能将数据写入双端口SRAM,方向0负责把SRAM内的数据读出。

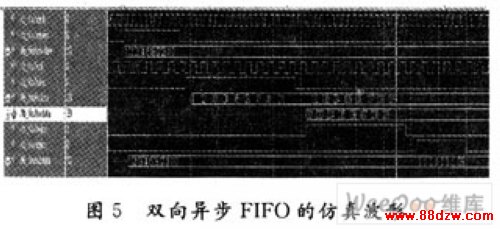

对于USB的控制端点,其接收的最大数据包为64 b。故本文设计的双向FIFO使用的sram亦为64 b。使用memory complier生成。图5是设计的双向FIFO在Modelsim下的仿真波形图。该波形显示了方向0写数据,方向1读数据和方向1写数据,方向0读数据的过程。

2.2 其他端点的优化设计

对于USB设备控制器的其他端点,由于其与控制端点有所不同。控制端点是一个双向端点,而非控制端点单向的传输。故对于非控制端点对应的缓冲区的容量设定,应使USB的带宽利用率尽量达到最高。由于USB规范中规定缓冲区必须有足够的空间,可以为全(高)速设备容纳一个时间片所能传输的数据量的两倍的容量。这样USB在处理一个数据分组的同时,可以接收下一个数据分组。以此种重叠技术可以提高总线利用率。如果批量端点的缓冲区的深度设计为1 024 B。就可以得到最大的带宽利用率。

《USB设备控制器端点缓冲区的优化技术设计》相关文章

- › USB设备控制器端点缓冲区的优化设计

- › USB设备控制器端点缓冲区的优化技术设计

- › USB设备驱动程序开发

- › C8051F320在USB设计中的应用

- › 一款集成HUB的USB设备控制器的设计

- › 让干电池为USB设备充电的小能量盒

- 在百度中搜索相关文章:USB设备控制器端点缓冲区的优化技术设计

- 在谷歌中搜索相关文章:USB设备控制器端点缓冲区的优化技术设计

- 在soso中搜索相关文章:USB设备控制器端点缓冲区的优化技术设计

- 在搜狗中搜索相关文章:USB设备控制器端点缓冲区的优化技术设计

当前位置:

当前位置: