USB设备控制器端点缓冲区的优化技术设计

[09-13 16:54:52] 来源:http://www.88dzw.com 接口定义 阅读:8680次

文章摘要:图6是其他端点所采用的双缓冲FIFO方案示意图。在状态1,req0控制访问FIFO0,reql控制访问FIFO1;在状态2,req0切换到访问FIFO1,req1切换到访问FIFO0。基于双缓冲FIFO的设计方案可使其他端点的带宽利用率达到最高,满足高速传输的需求。3 电路的ASIC实现结果对上述设计方案采用Verilog硬件描述语言进行设计。仿真工具为Modelsim SE 6.2b,前仿真通过后,对设计好的电路使用Design Complier进行综合。综合所使用的工艺库是SMIC 0.18 μm工艺库。对于控制端点,考虑到其主要处在SIE时钟和MCU时钟之间,对其所加的时钟约束分别为60

USB设备控制器端点缓冲区的优化技术设计,标签:接口技术,微机原理与接口技术,http://www.88dzw.com

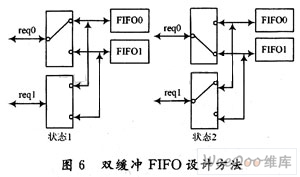

图6是其他端点所采用的双缓冲FIFO方案示意图。在状态1,req0控制访问FIFO0,reql控制访问FIFO1;在状态2,req0切换到访问FIFO1,req1切换到访问FIFO0。基于双缓冲FIFO的设计方案可使其他端点的带宽利用率达到最高,满足高速传输的需求。

3 电路的ASIC实现结果

对上述设计方案采用Verilog硬件描述语言进行设计。仿真工具为Modelsim SE 6.2b,前仿真通过后,对设计好的电路使用Design Complier进行综合。综合所使用的工艺库是SMIC 0.18 μm工艺库。

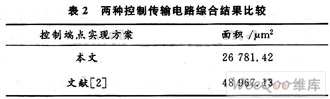

对于控制端点,考虑到其主要处在SIE时钟和MCU时钟之间,对其所加的时钟约束分别为60 MHz和30 MHz;此外还对传统的双缓冲FIFO结构进行了综合,两者所加约束完全一致。将两者的电路的综合结果对比如表2所示。

对比表2可知在保证控制端点功能的前提下,本文所采用的新型FIFO结构比传统双FIFO结构在电路的实现面积方面减小了45.3%。

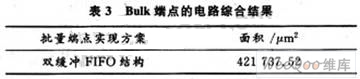

对于其他端点所采用的双缓冲FIFO方案保证了传输速度,但却是以牺牲面积为代价换来的。表3给出了批量(Bulk)传输端点(两个深度为512 B的FIFO)的实现面积报告。

4 结 语

USB设备控制器端点缓冲区的性能,直接关系到总线的带宽利用率。这里分析了USB的四种传输类型并根据其特点灵活的设计了不同的方案,并给出了最终电路的ASIC实现结果。特别是针对控制端点所提出的一种新方案具有一定的通用性,该方案可以应用在其他类似场合的设计中。

Tag:接口定义,接口技术,微机原理与接口技术,接口定义

《USB设备控制器端点缓冲区的优化技术设计》相关文章

- › USB设备控制器端点缓冲区的优化设计

- › USB设备控制器端点缓冲区的优化技术设计

- › USB设备驱动程序开发

- › C8051F320在USB设计中的应用

- › 一款集成HUB的USB设备控制器的设计

- › 让干电池为USB设备充电的小能量盒

- 在百度中搜索相关文章:USB设备控制器端点缓冲区的优化技术设计

- 在谷歌中搜索相关文章:USB设备控制器端点缓冲区的优化技术设计

- 在soso中搜索相关文章:USB设备控制器端点缓冲区的优化技术设计

- 在搜狗中搜索相关文章:USB设备控制器端点缓冲区的优化技术设计

分类导航

最新更新

当前位置:

当前位置: