ad9959应用控制电路

[11-20 17:31:49] 来源:http://www.88dzw.com 模拟电子技术 阅读:8488次

文章摘要:ad9959应用控制电路AD9959可以实现最多16电平的频率、相位和幅度调制,还可以工作在线性调频、调相或调幅模式。AD9959的应用范围包括相控阵列雷达/卢纳系统、仪表、同步时钟和RF信号源。AD9959的内部结构如图1所示,主要特性如下: ◇有4路带10位DAC的DDS通道,最高取样频率为500 MSPS; ◇大于65 dB的通道隔离度; ◇32位频率分辨率; ◇14位相位失调分辨率; ◇10位输出幅度可缩放的分辨率; ◇具有增强数据吞吐量的串行I/O口(SPI); ◇可软件/硬件控制以降低功耗; ◇双电源(DDS核1.8 V,

ad9959应用控制电路,标签:模拟电子技术基础,模拟电子电路,http://www.88dzw.comad9959应用控制电路

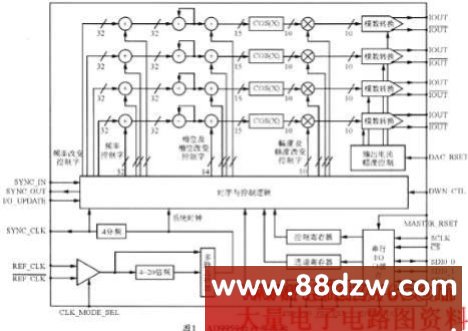

AD9959可以实现最多16电平的频率、相位和幅度调制,还可以工作在线性调频、调相或调幅模式。AD9959的应用范围包括相控阵列雷达/卢纳系统、仪表、同步时钟和RF信号源。AD9959的内部结构如图1所示,主要特性如下:

◇有4路带10位DAC的DDS通道,最高取样频率为500 MSPS;

◇大于65 dB的通道隔离度;

◇32位频率分辨率;

◇14位相位失调分辨率;

◇10位输出幅度可缩放的分辨率;

◇具有增强数据吞吐量的串行I/O口(SPI);

◇可软件/硬件控制以降低功耗;

◇双电源(DDS核1.8 V,串行I/O3.3 V);

◇内置多器件同步功能;

◇内置时钟倍频锁相环(4~20倍倍频)。

2 AD9959的引脚功能

AD9959采用56脚LFCSP封装,各引脚的功能定义如下:

SYNC_IN:输入引脚,可同步多片AD9959。使用时应与主AD9959的SYNC_OUT相连;

SYNC_OUT:输出引脚,可同步多片AD9959,使用时应与从AD9959的SYNC_IN相连;

MASTER_RESET:复位输入引脚,高有效;

PWR_DWN_CTL:外部电源掉电控制引脚;

AGND:模拟地;

DVDD:数字电源(1.8 V);

DGND:数字地;

DAC_RSET:输入引脚,可为DAC设置参考电流,使用时应通过一个1.91 kΩ电阻接地;

REF_CLK和REF_CLK:参考时钟或振荡输入端(互补输入),如果使用单端输入方式,则应从REF_CLK引脚连接一个0.1μF的解耦电容到 AVDD或AGND;

CLK_MODE_SEL:振荡器部分控制引脚,接高电平时,电压不要超过1.8 V,接低电平时,振荡器被旁路;

LOOP_FILTER:输入端,使用时应串联一个零电阻和680 pF电容至最近的AVDD脚(Pin28);

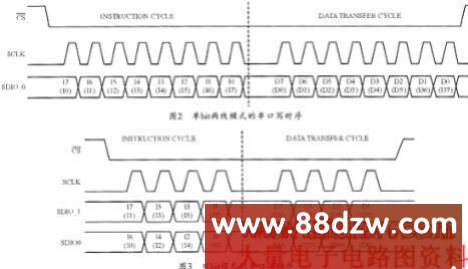

I/O_UPDATE:输入引脚,通过该脚的上升沿可把串行口缓存的数据内容送至激活的寄存器中,I/O_UPDATE信号应与SYNC_CLK信号保持同步,并须满足建立时间与保持时间的要求;

CS:片选串口使能信号端,低有效;

DVDD_I/O:3.3 V数字电源;

SYNC_CLK:时钟输出,为内部时钟的1/4,用于同步I/O_UPDATE信号;

SCLK:I/O串行操作时钟输入端,在该端的上升沿写入数据,下降沿读出数据;

SDIO_0:双向引脚,用于串行操作的数据输入和输出;

SDIO_1:3:双向引脚,用于串行操作数据输入输出,也可用于控制DAC输出幅度的斜率;

P0~P3:输入引脚,这四个引脚用于控制调制方式的选择,扫描累加器的开关或者输出幅度的升降斜率。该四个引脚中的任何一个引脚信号的变化都等同于一个I/O_UPDATE信号的上升沿,该端须与SYNC_CLK信号保持同步,并须满足建立时间与保持时间的要求;

CH0_IOUT ~CH3_IOUT, CH0_IOUT ~CH3_IOUT:输出引脚,四个通道的互补输出端,使用时,需接上拉电阻至AVDD。

3 工作模式组合

- 上一篇:单电源仪表放大器电路图

《ad9959应用控制电路》相关文章

- › 基于AD9951射频正弦波信号发生器的设计

- › ad9959应用控制电路

- 在百度中搜索相关文章:ad9959应用控制电路

- 在谷歌中搜索相关文章:ad9959应用控制电路

- 在soso中搜索相关文章:ad9959应用控制电路

- 在搜狗中搜索相关文章:ad9959应用控制电路

当前位置:

当前位置: