基于RF2.4 GHz的超低功耗无线数传系统设计

[09-14 00:27:37] 来源:http://www.88dzw.com 通信电路 阅读:8717次

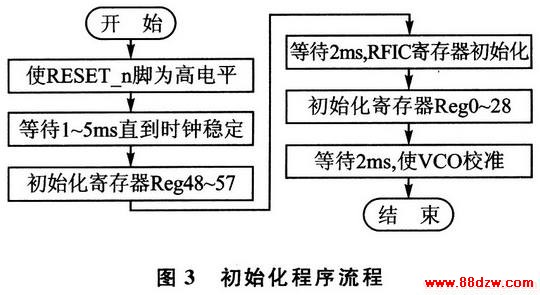

文章摘要: 系统上电后,先使EMl98810的RESET_n引脚为低电平,以保证芯片有效复位;再使此引脚为高电平,BRCLK脚会产生12 MHz的时钟;然后进行相关寄存器初始化。初始化程序流程如图3所示。 其中,Reg48为数据帧格式配置寄存器,需要设置前导区的长度(默认为3字节),同步字长度默认为64位,前导尾默认长度为4位,数据默认为NRZ格式。该寄存器的第2位为1则配置为睡眠模式,第3位为1则配置为待机模式。Reg49~51用于设置发射和接收的延迟时间。Reg52~55用于设置同步控制字,默认全部为0000H。Reg57用于配置是否启用CRC校验、包长度控制方式等。Reg48~57详细

基于RF2.4 GHz的超低功耗无线数传系统设计,标签:电路设计,http://www.88dzw.com系统上电后,先使EMl98810的RESET_n引脚为低电平,以保证芯片有效复位;再使此引脚为高电平,BRCLK脚会产生12 MHz的时钟;然后进行相关寄存器初始化。初始化程序流程如图3所示。

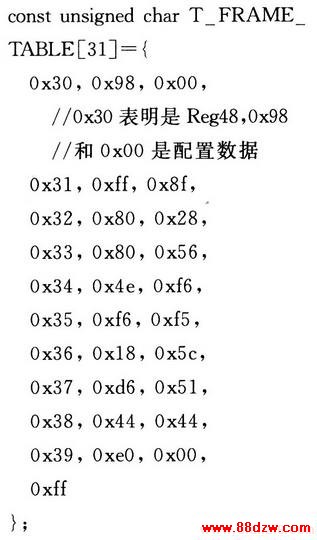

其中,Reg48为数据帧格式配置寄存器,需要设置前导区的长度(默认为3字节),同步字长度默认为64位,前导尾默认长度为4位,数据默认为NRZ格式。该寄存器的第2位为1则配置为睡眠模式,第3位为1则配置为待机模式。Reg49~51用于设置发射和接收的延迟时间。Reg52~55用于设置同步控制字,默认全部为0000H。Reg57用于配置是否启用CRC校验、包长度控制方式等。Reg48~57详细配置数据如下:

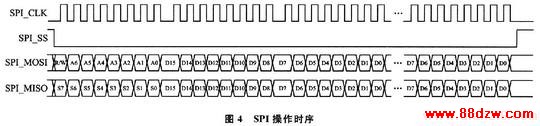

Reg0~28初始化完成后再延时2 ms,就可以直接进行数据的收发了。特别要注意的是,帧寄存器Reg48~57必须在RFIC寄存器Reg0~28之前初始化。所有寄存器读写和收发的数据都是通过SPI接口进行的,并且只支持从模式,SPI操作时序如图4所示。在芯片第28脚LDO_TUNE接地时(R1断开,R2接O Ω电阻),其数据在SPI_CLK时钟的上升沿有效;当LDO_TUNE接VDD时(R2断开,R1接0 Ω电阻),数据在SPI_CLK时钟的下降沿有效。只要SPI_SS为高电平,寄存器中的数据就保持不变;只有SPI_SS为低电平时,才能重新改写寄存器中的内容。

EMl98810有两种检测收发数据包长度的方法:一种是自动在数据帧内检测出来,最大帧长度不能超过255字节。先设置Reg57的第13位为1,则发送或接收数据区中的第1个字节就代表数据的长度,帧控制器会自动控制收发开始与停止。另外一种是保持发射或接收的状态不变,通过外接MSP430F247来控制数据包的正确发送与接收。

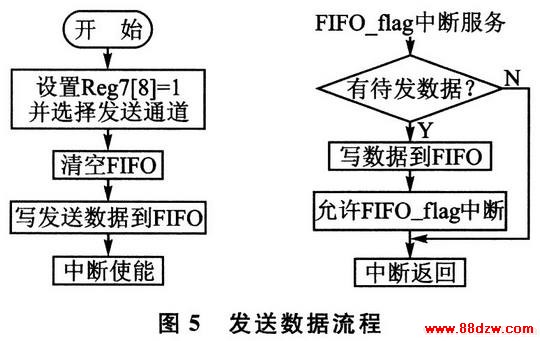

发送数据流程如图5所示。在发射数据时,先设置Reg7的第8位为1,允许在内部状态机控制下进入数据发射状态,再设置Reg7的O~6位为所选通道。在发送前导尾区数据前,MSP430F247必须将数据放人FIFO中,如果数据长度超过63字节,应该分多次写入。FIFO_flag=1表示FIFO为空,MSP430F247利用此信号作为中断请求,保证发送数据写入FIF0的实时性,在数据发送完成后PKT_flag=1。

如果设置Reg7[7]=1和Reg7[O~6]为与发射相同的通道,则芯片进入自动接收状态,接收数据流程如图6所示。当检测到同步字后会自动进行数据包的接收解码,接收完成后进入待机模式。如果接收数据超过63字节,则有FIFO_flag=1,MSP430F247利用此信号作中断请求以保证读出数据的实时性。

Tag:通信电路,电路设计,家电维修 - 单元电路介绍 - 通信电路

- 上一篇:自制2.4G全向天线的制作方法

《基于RF2.4 GHz的超低功耗无线数传系统设计》相关文章

- › 基于RF2.4 GHz的超低功耗无线数传系统设计

- 在百度中搜索相关文章:基于RF2.4 GHz的超低功耗无线数传系统设计

- 在谷歌中搜索相关文章:基于RF2.4 GHz的超低功耗无线数传系统设计

- 在soso中搜索相关文章:基于RF2.4 GHz的超低功耗无线数传系统设计

- 在搜狗中搜索相关文章:基于RF2.4 GHz的超低功耗无线数传系统设计

最新更新

当前位置:

当前位置: