基于CPLD的频谱电平显示电路设计与实现

[09-12 18:26:17] 来源:http://www.88dzw.com EDA/PLD 阅读:8157次

文章摘要:摘要:本文基于VHDL硬件描述语言,利用CPLD器件EPM570T100C5和LED点阵屏实现了对音频信号的频谱显示,给出了设计过程、VHDL语言源程序和实验结果,拓展了CPLD在显示领域的应用。1.引言LED点阵显示屏具有醒目、动态效应好、省电节能、亮度较高、用途广等优点,是现代 化城市的主要标志之一。笔者利用VHDL硬件描述语言设计了以CPLD器件为核心的控制电路, 在LED点阵屏上实现了音频信号的频谱型电平动态显示, 而且具有显示模式多样化、易编程 修改,颜色可变、动态效果好等优点。2.系统组成本设计所用的EPM570T100C5采用了Altera公司的MAXII (Multiple A

基于CPLD的频谱电平显示电路设计与实现,标签:eda技术,eda技术实用教程,http://www.88dzw.com摘要:本文基于VHDL硬件描述语言,利用CPLD器件EPM570T100C5和LED点阵屏实现了对音频信号的频谱显示,给出了设计过程、VHDL语言源程序和实验结果,拓展了CPLD在显示领域的应用。

1.引言

LED点阵显示屏具有醒目、动态效应好、省电节能、亮度较高、用途广等优点,是现代 化城市的主要标志之一。笔者利用VHDL硬件描述语言设计了以CPLD器件为核心的控制电路, 在LED点阵屏上实现了音频信号的频谱型电平动态显示, 而且具有显示模式多样化、易编程 修改,颜色可变、动态效果好等优点。

2.系统组成

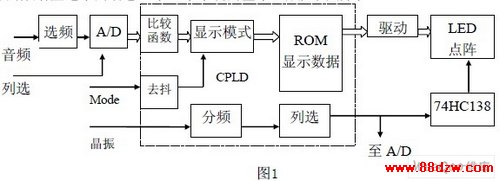

本设计所用的EPM570T100C5采用了Altera公司的MAXII (Multiple Array Matrix II) 系列器件作为目标CPLD,采用双色8*8LED点阵作为终端显示器件,配合一些必需的外围器件 和电路,实现了对音频信号的选频、AD转换、各频段的电平显示模式控制、最终实现了音频 信号的频谱型电平的动态显示。本系统的基本组成如图1所示:

2.1 音频输入与预处理模块

由于本设计采用8个频段电平显示,因此,笔者对音频信号进行了8个中心频率分别为 100Hz、200Hz、500Hz、1000Hz、1500Hz、3000Hz、6000Hz、12000Hz的带通电路的选频处理, 经电压保持电路后送至以ADC0809为核心的八通道8位输出数模转换电路,由于ADC0809具有 八个输入通道,受CPLD输出的列选信号控制,从而实现了LED的八根列选线(共阴极)分别 对应音频信号的8个中心频率,为频谱型电平显示实现了列选扫描控制。

由于列选信号的切换频率设定为200Hz,即频段切换周期为5ms,ADC0809 完全能够胜 任音频信号各频段直流电平的A/D 转换处理,因此,ADC0809 一直处于主动转换状态,无需 接受CPLD 芯片的转换控制。

2.2 核心控制模块

本设计的核心模块采用Altera公司的CPLD器件,型号为EPM570T100C5,它基于突破性的 CPLD架构,提供业界所有CPLD系列中单个I/O管脚最低成本和最小功耗。这些器件采用新的 查表(LUT)体系,采用TSMC的0.18μm嵌入Flash工艺,使其裸片尺寸仅为同样工艺器件的1/4, 而且包括非易失性Flash存储模块和JTAG控制电路。

本电路采用12MHz的有源晶振,为CPLD提供主时钟。EPM570T100C5芯片主要集成了分频、 列选扫描、按键去抖、数字电平信号的线性比较、显示模式控制、显示数据ROM等功能模块。

分频电路对12MHz时钟信号进行分频处理后得到200Hz的列选计数脉冲,送至74HC138译 码器的输入端和ADC0809的通道地址选择控制端,实现8*8LED点阵的列扫描动态控制和 ADC0809的通道选择控制。

按照人眼的视觉习惯,线性比较电路主要负责将A/D转换后的8位数据电平信号(共256 个组态)转换为8个梯级的数据信号,经显示模式控制电路处理后作为地址数送至显示数据 ROM,从而直接调用ROM中寄存的显示模式数据。

2.3 输出与显示模块

本设计采用双色(红色和绿色)8*8LED 点阵作为终端显示器件,在CPLD 的ROM 数据控 制下,8*8LED 点阵的每个像素点能产生红色、绿色、$(红绿混合色),能够再现颜色 的多样化。

由于一般的I/O 的驱动能力是有限的,CPLD 中的ROM 输出的显示数据需要经过驱动电 路后送至8*8LED 点阵的行选端(阳极),列选线(阴极)则受74HC138 输出的低电平译码 信号的控制。

3.软件设计

本设计采用Altera 公司的Quartus II 7.0 (32-Bit)集成开发系统,它具有简洁、合 理的操作界面,多语言支持的环境及其高效代码生成编译内核使得所有的设计输人、编译、 综合和仿真都可以在项目管理器中完成。另外,QuartusⅡ7.0 (32-Bit)支持几乎所有的FPGA 和CPLD 芯片,与MATLAB 和DSP Builder 结合可以进行基于FPGA 的DSP 系统开发,是DSP 硬件系统实现的关键EDA 工具,与SOPC Builder 结合,可实现SOPC 系统开发,是一款较受 用户欢迎的开发工具。

本文采用VHDL 语言作为硬件描述语言,采用自顶向下的层次化设计方法。为了突出各 模块之间的连接关系,顶层模块(Top.tdf)采用原理图方式对各个功能模块进行综合和调 用,如图2 所示。

《基于CPLD的频谱电平显示电路设计与实现》相关文章

- › 基于CPCI总线的多网口卡设计

- › 一种基于CPLD的声发射信号传输系统设计

- › 基于CPLD的臭氧电源控制系统的软硬件设计

- › 基于CPLD/FPGA的CMI编码设计与实现

- › 基于CPLD的压电生物传感器检测电路设计

- › 基于CPLD的CCD信号发生器的研究

- 在百度中搜索相关文章:基于CPLD的频谱电平显示电路设计与实现

- 在谷歌中搜索相关文章:基于CPLD的频谱电平显示电路设计与实现

- 在soso中搜索相关文章:基于CPLD的频谱电平显示电路设计与实现

- 在搜狗中搜索相关文章:基于CPLD的频谱电平显示电路设计与实现

当前位置:

当前位置: