基于改进型二步索引算法OSD电路的FPGA实现

[09-12 18:26:45] 来源:http://www.88dzw.com EDA/PLD 阅读:8982次

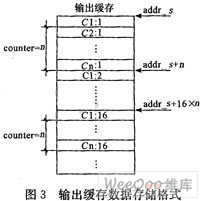

文章摘要:在二步索引算法中,引入了行显示字符数li和菜单显示字符行数nk2个参数,通过nk首先索引菜单中第i行的显示字符数li,根据li控制索引该行第j个字符编号Ni×j。根据li可以知道每行显示的字符数,所以字符编码信息可以按行顺序紧密的存储,即每行存储的数据采用非定长的方式,如图1(b)所示。与图1(a)所示的逐字索引法存储器结构相比,二步索引法在对存储器资源的节省方面效果是显著的。2 二步索引法OSD电路结构实现2.1 字符索引电路实现如图3所示,相比于逐字索引法的电路实现结构,二步索引法的电路实现结构中增加了字符行寄存器和用于存放行字符数信息的存储器。字符行寄存器中存人nk,根据字符行计数器所计

基于改进型二步索引算法OSD电路的FPGA实现,标签:eda技术,eda技术实用教程,http://www.88dzw.com在二步索引算法中,引入了行显示字符数li和菜单显示字符行数nk2个参数,通过nk首先索引菜单中第i行的显示字符数li,根据li控制索引该行第j个字符编号Ni×j。根据li可以知道每行显示的字符数,所以字符编码信息可以按行顺序紧密的存储,即每行存储的数据采用非定长的方式,如图1(b)所示。与图1(a)所示的逐字索引法存储器结构相比,二步索引法在对存储器资源的节省方面效果是显著的。

2 二步索引法OSD电路结构实现

2.1 字符索引电路实现

如图3所示,相比于逐字索引法的电路实现结构,二步索引法的电路实现结构中增加了字符行寄存器和用于存放行字符数信息的存储器。字符行寄存器中存人nk,根据字符行计数器所计数据与nk比较来控制从行字符数存储器中读出的数据数。读出的行字符数信息li再用以控制显示第i行菜单字符所需从字符编码存储器中读出的字符编码数据数。读出的字符编码Ni×j通过地址生成电路转换成相应字符的点阵信息在字符点阵ROM中存储地址段的首地址,从而在字符点阵ROM中索引出相应字符的点阵数据,如此反复,可实现对全部字符点阵数据的索引。

2.2 数据输出控制与层混合叠加电路实现

从字符点阵ROM中读取出的字符点阵信息经过点阵重组电路的处理后将按字符Cl×Ch顺序的点阵信息转换成按菜单行顺序的格式存入到输出缓存中。输出缓存中数据的存储顺序如图3所示。

输出缓存能够存储整幅菜单的显示信息,以使菜单生成和菜单输出显示2个过程相互独立,从而使得在显示菜单的同时,可进行新菜单内容的读入,保证菜单显示的连贯胜。输出缓存容量大小由包含显示信息最多的一幅菜单决定。

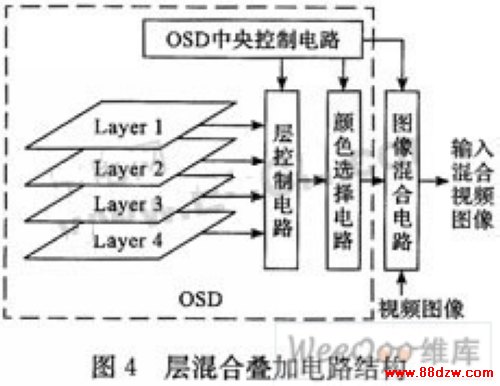

从输出缓存中读出的数据用于控制生成菜单字符层,在层选择电路中与菜单背景层和属性条层进行叠加处理后输出一幅完整的菜单。字符层、菜单背景层和属性条层相互独立,由层混合控制电路控制进行混合叠加处理,再将菜单与屏幕背景层进行叠加输出混合视频信号。层混合叠加电路的实现结构如图4所示。

3 OSD电路的FPGA实现及功能验证

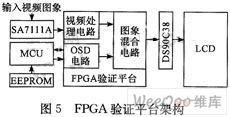

设计在Xilinx公司的ISE6.3软件环境下,使用Verilog HDL硬件描述语言对其电路逻辑进行描述,并以Xilinx公司xc2v1500bg575-4型为核心芯片的FPGA仿真验证平台对其进行硬件实现及功能验证。FPGA验证平台架构如图5所示。

验证平台输入模拟视频信号,经SAA7111A芯片电路A/D采样转变为数字视频信号接入FPGA验证平台。经过视频处理电路去隔行、尺寸缩放等处理的视频信号在图象混合电路中与OSD菜单混合后输出经DS90C38芯片电路转为LVDS(低压差分信号)信号并驱动液晶屏显示结果。

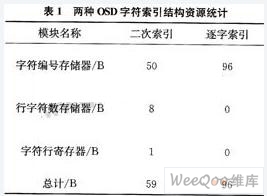

对2种字符索引算法下实现的OSD电路进行验证比较。OSD字符索引电路部分使用到的存储器资源可以分为字符编码存储器、行字符数存储器、字符行寄存器3种。以生成图6中所示菜单为例分析2种算法下OSD字符索引电路对存储器资源的使用情况,将结果列于表1中。

《基于改进型二步索引算法OSD电路的FPGA实现》相关文章

- › 基于改进型二步索引算法OSD电路的FPGA实现

- 在百度中搜索相关文章:基于改进型二步索引算法OSD电路的FPGA实现

- 在谷歌中搜索相关文章:基于改进型二步索引算法OSD电路的FPGA实现

- 在soso中搜索相关文章:基于改进型二步索引算法OSD电路的FPGA实现

- 在搜狗中搜索相关文章:基于改进型二步索引算法OSD电路的FPGA实现

当前位置:

当前位置: