基于CPLD器件在时间统一系统中的应用

[09-12 18:28:00] 来源:http://www.88dzw.com EDA/PLD 阅读:8574次

文章摘要:图8 计数器模块 function ImgZoom(Id)//重新设置图片大小 防止撑破表格 { var w = $(Id).width; var m = 650; if(w缓冲电路它的功能是将计数器输出的5组时间信号以B码的格式交替输出。缓冲电路生成的模块如图 9所示。图9 缓冲电路模块图为简单起见,用VHDL语言描述如下:t2模块是由计数器和缓冲电路合成的较高层的模块。这个模块的功能是置数后计数器从此时刻开始按秒计数,将时间信号以B码的格式并行输出。两个模块的连接情况如图10所示,t2模块如图 11 所示。图10 t2模块内部电路图11 t2模块(2)t1模块并串转换电路由于B码是串行码,

基于CPLD器件在时间统一系统中的应用,标签:eda技术,eda技术实用教程,http://www.88dzw.com

图8 计数器模块 function ImgZoom(Id)//重新设置图片大小 防止撑破表格 { var w = $(Id).width; var m = 650; if(w

缓冲电路

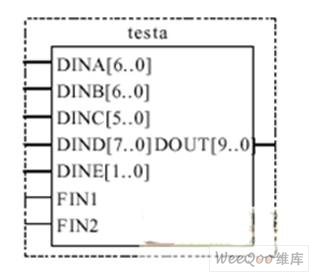

它的功能是将计数器输出的5组时间信号以B码的格式交替输出。缓冲电路生成的模块如图 9所示。

图9 缓冲电路模块图

为简单起见,用VHDL语言描述如下:

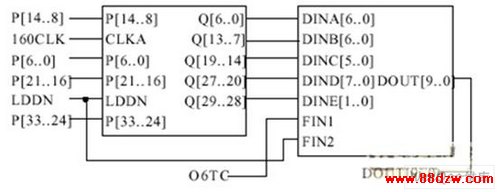

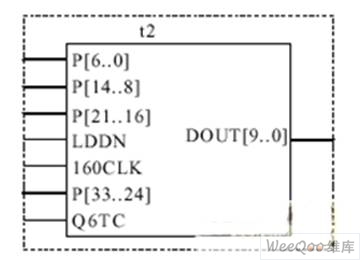

t2模块是由计数器和缓冲电路合成的较高层的模块。这个模块的功能是置数后计数器从此时刻开始按秒计数,将时间信号以B码的格式并行输出。两个模块的连接情况如图10所示,t2模块如图 11 所示。

图10 t2模块内部电路

图11 t2模块

(2)t1模块

并串转换电路

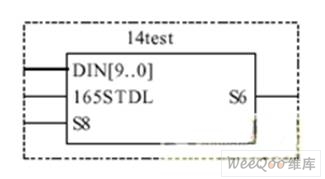

由于B码是串行码,须将t1模块输出的并行数据进行并串转换。并串转换电路生成的模块如图 12 所示。

图12 并串转换电路模块 function ImgZoom(Id)//重新设置图片大小 防止撑破表格 { var w = $(Id).width; var m = 650; if(w

时序脉冲发生器

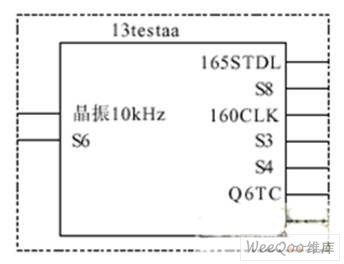

该部分电路主要由七个脉冲分配器相级联和一些逻辑门控制组成。完成的主要功能有:产生B码的3种脉冲形式;提供计数器的时钟--"S"信号;提供缓冲电路中计数器的时钟--周期100ms;提供并串转换电路的置位信号。时序脉冲发生器生成的模块如图 13所示。

图13 时序脉冲发生器模块

t1模块是并串转换电路和时序脉冲发生器合成的较高层的模块。这个模块的功能是将t2模块输出的并行时间码串行输出,由时序脉冲发生器输出各种控制信号对串行码控制输出B码的三类脉冲,同时输出t2模块所需的各类时钟信号。并串转换电路模块和时序脉冲发生器模块的连接情况见图14,t1模块见图 15。

图14 t1模块内部电路

图15 t1模块

(3)t3模块

t3模块是由t1、t2两个模块构成的最顶层的模块,其内部连接如图16所示。

- 上一篇:FPGA与CPLD的辨别和分类

《基于CPLD器件在时间统一系统中的应用》相关文章

- › 基于CPCI总线的多网口卡设计

- › 一种基于CPLD的声发射信号传输系统设计

- › 基于CPLD的臭氧电源控制系统的软硬件设计

- › 基于CPLD/FPGA的CMI编码设计与实现

- › 基于CPLD的压电生物传感器检测电路设计

- › 基于CPLD的CCD信号发生器的研究

- 在百度中搜索相关文章:基于CPLD器件在时间统一系统中的应用

- 在谷歌中搜索相关文章:基于CPLD器件在时间统一系统中的应用

- 在soso中搜索相关文章:基于CPLD器件在时间统一系统中的应用

- 在搜狗中搜索相关文章:基于CPLD器件在时间统一系统中的应用

当前位置:

当前位置: