基于CPLD器件在时间统一系统中的应用

[09-12 18:28:00] 来源:http://www.88dzw.com EDA/PLD 阅读:8574次

文章摘要:图16 t3模块内部电路图由图16可见,t3模块(图17)将所有内部电路集成,整个电路只有32个输入端,3个输出端。将t3模块直接烧入可编程芯片即可。图17 t3模块 function ImgZoom(Id)//重新设置图片大小 防止撑破表格 { var w = $(Id).width; var m = 650; if(w3.3 码合成电路可编程芯片输出了组成B码的3个分信号,经过1个或门后将3个信号合成了B码信号,如图18所示。图18 合成B码波形图结语本设计的难点在于如何正确地安排好芯片内部各个模块之间的时序。该B码源通过解调之后能够显示正确的时间,达到了很好的效果。该B码源最大的特点是电

基于CPLD器件在时间统一系统中的应用,标签:eda技术,eda技术实用教程,http://www.88dzw.com

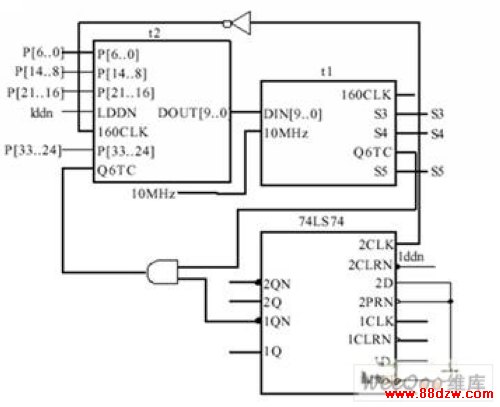

图16 t3模块内部电路图

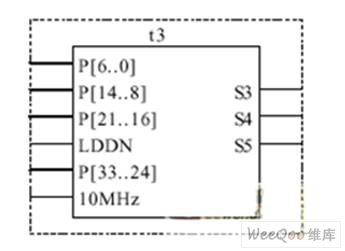

由图16可见,t3模块(图17)将所有内部电路集成,整个电路只有32个输入端,3个输出端。将t3模块直接烧入可编程芯片即可。

图17 t3模块 function ImgZoom(Id)//重新设置图片大小 防止撑破表格 { var w = $(Id).width; var m = 650; if(w

3.3 码合成电路

可编程芯片输出了组成B码的3个分信号,经过1个或门后将3个信号合成了B码信号,如图18所示。

图18 合成B码波形图

结语

本设计的难点在于如何正确地安排好芯片内部各个模块之间的时序。该B码源通过解调之后能够显示正确的时间,达到了很好的效果。该B码源最大的特点是电路非常简单,可靠性较高。通过可编程芯片高度集成了一个系统,克服了以往B码源电路复杂的缺点。

Tag:EDA/PLD,eda技术,eda技术实用教程,EDA/PLD

- 上一篇:FPGA与CPLD的辨别和分类

《基于CPLD器件在时间统一系统中的应用》相关文章

- › 基于CPCI总线的多网口卡设计

- › 一种基于CPLD的声发射信号传输系统设计

- › 基于CPLD的臭氧电源控制系统的软硬件设计

- › 基于CPLD/FPGA的CMI编码设计与实现

- › 基于CPLD的压电生物传感器检测电路设计

- › 基于CPLD的CCD信号发生器的研究

- 在百度中搜索相关文章:基于CPLD器件在时间统一系统中的应用

- 在谷歌中搜索相关文章:基于CPLD器件在时间统一系统中的应用

- 在soso中搜索相关文章:基于CPLD器件在时间统一系统中的应用

- 在搜狗中搜索相关文章:基于CPLD器件在时间统一系统中的应用

分类导航

最新更新

当前位置:

当前位置: