直扩导航系统中数字科思塔斯环的FPGA设计与实现

[09-12 18:29:06] 来源:http://www.88dzw.com EDA/PLD 阅读:8442次

文章摘要:引言扩频接收机载波的同步包括捕获和跟踪两个过程,载波捕获即多普勒频移的粗略估计通常包含在伪码同步过程中,而精确的载波相位及多普勒频移则通过FLL(锁频环)和PLL(锁相环)跟踪来实现。锁频环直接跟踪载波频率,而锁相环则直接对载波相位进行跟踪。锁相环具有较高的跟踪精度,但对通信链路干扰的容忍能力差,特别是受载体动态引入的多普勒频移影响较大;而锁频环具有较好的动态性能,但跟踪精度较低。载波跟踪环的跟踪精度决定了最后定位测量的精度。常规接收机中载波跟踪是在数字延迟锁定环对伪码相关解扩的基础上,通过科斯塔斯环(PLL的一种)重构载波相位解调BPSK数据实现的。当多普勒频移高于±40kHz ,多普勒频率

直扩导航系统中数字科思塔斯环的FPGA设计与实现,标签:eda技术,eda技术实用教程,http://www.88dzw.com引言

扩频接收机载波的同步包括捕获和跟踪两个过程,载波捕获即多普勒频移的粗略估计通常包含在伪码同步过程中,而精确的载波相位及多普勒频移则通过FLL(锁频环)和PLL(锁相环)跟踪来实现。锁频环直接跟踪载波频率,而锁相环则直接对载波相位进行跟踪。锁相环具有较高的跟踪精度,但对通信链路干扰的容忍能力差,特别是受载体动态引入的多普勒频移影响较大;而锁频环具有较好的动态性能,但跟踪精度较低。载波跟踪环的跟踪精度决定了最后定位测量的精度。常规接收机中载波跟踪是在数字延迟锁定环对伪码相关解扩的基础上,通过科斯塔斯环(PLL的一种)重构载波相位解调BPSK数据实现的。当多普勒频移高于±40kHz ,多普勒频率一次变化率为4kHz/s ,二次变化率为200Hz/s2时,接收机的PLL将不能稳定工作。由于在系统设计中,多普勒频移远小于这一极限值,另外,锁频环鉴别器需要两组相关积分采样点用于计算频率差值,并且这两组采样值应该在同一个数据位时间区间之内。系统中,由于积分时间与调制数据位宽度相同,每次得到的相关采样值将位于不同的数据位区间内,不适合使用锁频环,故只采用科斯塔斯环完成载波频率和相位的跟踪。

环路原理

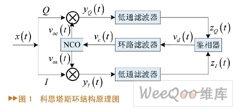

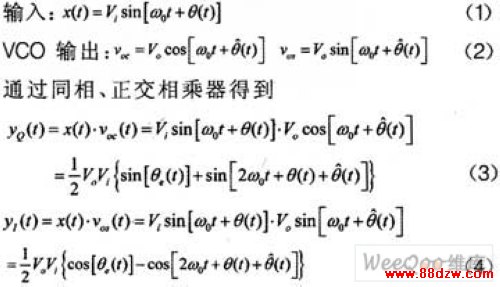

科思塔斯载波跟踪环由载波鉴相器、载波环路滤波器和载波NCO组成。其结构原理图如图1所示。

环路实现

载波NCO的FPGA设计

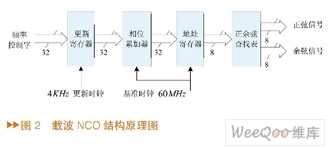

载波NCO是载波跟踪环的重要组成部分,它的主要功能是产生本地复制载波信号。载波NCO主要由相位累加器、地址寄存器和正弦查找表构成。结构原理如图2所示。

载波NCO设置有频率控制字输入口,相位累加器对输入的控制字进行累加,累加结果的高8位作为查询表的地址,通过查询预先存设的正余弦表,输出两路信号,其中一路与载波同相,另一路与载波正交。载波环路通过不断调整载波NCO的频率控制字来保持对接收信号载波频率和相位的跟踪。载波NCO要有足够的频率分辨率,保证能高精度跟踪载波,这就要求载波NCO要有足够的相位累加器字长。本设计中累加字长取为32位,累加时钟为60MHz,要求输出频率为50MHz,可以得到频率控制字为:

频率分辨率为: 即通过输入频率控制字来改变输出正/余弦信号的频率时,可以达到0.014Hz的最小步进。另外,也可以根据实际需要的频率改变输入频率控制字值。

即通过输入频率控制字来改变输出正/余弦信号的频率时,可以达到0.014Hz的最小步进。另外,也可以根据实际需要的频率改变输入频率控制字值。

首先在Matlab中仿真一个周期的正余弦波形,由于取8位输出,所以一个周期应该取28个点,均匀取256个点作为一个周期数据。在FPGA中调用ROM单元,存储这256个点值,作为查找表。根据图1的结构原理在FPGA中设计顶层框图如图3所示。图中,sin_rom和cos_rom为正余弦查找表。频率控制字输入在累加器中累加,取累加结果的高8位作为查询地址,在工程中调用sin_rom和cos_rom模块,得到正余弦输出信号。在FPGA中对设计进行仿真,仿真输入控制字为20000000。下载到FPGA中可得到SignalTap II测试结果。仿真和测试结果(图略)验证了设计的正确性。

《直扩导航系统中数字科思塔斯环的FPGA设计与实现》相关文章

- › 直扩导航系统中数字科思塔斯环的FPGA设计与实现

- 在百度中搜索相关文章:直扩导航系统中数字科思塔斯环的FPGA设计与实现

- 在谷歌中搜索相关文章:直扩导航系统中数字科思塔斯环的FPGA设计与实现

- 在soso中搜索相关文章:直扩导航系统中数字科思塔斯环的FPGA设计与实现

- 在搜狗中搜索相关文章:直扩导航系统中数字科思塔斯环的FPGA设计与实现

当前位置:

当前位置: