利用FPGA的新功能保证视频设计安全性

[09-12 18:30:18] 来源:http://www.88dzw.com EDA/PLD 阅读:8543次

文章摘要:用户定义的算法可以如系统所需要的一样简单或复杂 - 例如:可以是简单的哈希算法,或者更为复杂的三次DES、AES6?、128或256位,甚至是完全定制的算法。同时还可以将用户定义的认证算法集成到接收器的认证流程内部。这样可以进一步将接收单元与视频流系统、设计与特定的接收单元捆绑在一起,从而进一步提高抵抗克隆的安全能力。此外,算法可以改变以支持不同的视频解密协议配置,甚至在不同型号或不同代产品间采用不同的算法,从而进一步保证安全性。安全性提高对生产的影响硬件安全性问题同样适用于生产流程,特别是板级测试和验证。因此,设计中经常将JTAG功能移除,因为JTAG功能易使设计导致反向工程。许多企业都采用

利用FPGA的新功能保证视频设计安全性,标签:eda技术,eda技术实用教程,http://www.88dzw.com用户定义的算法可以如系统所需要的一样简单或复杂 - 例如:可以是简单的哈希算法,或者更为复杂的三次DES、AES6?、128或256位,甚至是完全定制的算法。同时还可以将用户定义的认证算法集成到接收器的认证流程内部。这样可以进一步将接收单元与视频流系统、设计与特定的接收单元捆绑在一起,从而进一步提高抵抗克隆的安全能力。此外,算法可以改变以支持不同的视频解密协议配置,甚至在不同型号或不同代产品间采用不同的算法,从而进一步保证安全性。

安全性提高对生产的影响

硬件安全性问题同样适用于生产流程,特别是板级测试和验证。因此,设计中经常将JTAG功能移除,因为JTAG功能易使设计导致反向工程。许多企业都采用JTAG来缩短测试时间并提高测量和验证流程中的系统测试覆盖范围。然而,没有JTAG,就需要更多的测试,特别是系统级测试来保证一定的测试覆盖范围。不使用JTAG技术会提高生产成本,并最终影响到系统总成本。

JTAG的问题在于INTEST命令,用于检查设计的内部逻辑功能。反向工程时,这一命令可用来判断设计的功能。图3给出了一个简单的例子,其中数据移入寄存器,执行INTEST命令,这样数据会在时钟作用下移入逻辑构造,进入下一寄存器,结果可以被读出。由于可将总体设计的复杂度缩小到更小的逻辑模块,因此这一命令可使反向工程的工作更容易。

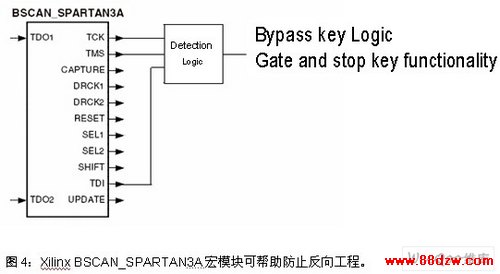

一些FPGA平台可帮助防止发生这一过程,同时仍然允许生产商完成其管脚至管脚(pin-to-pin)功能。例如,在Xilinx? Spartan?-3A 平台中, 可在设计中使用BSCAN_SPARTAN3A宏模块,其检测逻辑可监控FPGA构造中的JTAG控制信号,如图4所示。如果检测到JTAG控制信号的活动,用户在设计可以立即绕过关键逻辑或关断关键功能,不再执行正确的功能。这样反向工程人员读到的将是不正确的功能模块,在不能完成预期功能的解决方案上浪费时间和资源。

支持DeviceDNA的FPGA平台可保证视频接收机的设计安全,同时还可为测试和验证流程提供支持,从而能够提供成本经济的高质量安全解决方案,支持多种不同的视频流加密协议。欲了解更多DeviceDNA或JTAG的详细信息,请登陆www.xilinx.com/cn参考《Spartan-3系列配置用户手册》。(Mark Moran,通用产品部高级战略营销经理, 赛灵思)

《利用FPGA的新功能保证视频设计安全性》相关文章

- › 利用FPGA协处理器提升无线子系统的性能

- › 利用FPGA协处理提升无线子系统性能

- › 利用FPGA实现视频监控系统的视频处理

- › 利用FPGA实现低成本汽车多总线桥接

- › 利用FPGA和CPLD数字逻辑实现ADC

- › 利用FPGA实现高性能数字电视系统

- 在百度中搜索相关文章:利用FPGA的新功能保证视频设计安全性

- 在谷歌中搜索相关文章:利用FPGA的新功能保证视频设计安全性

- 在soso中搜索相关文章:利用FPGA的新功能保证视频设计安全性

- 在搜狗中搜索相关文章:利用FPGA的新功能保证视频设计安全性

当前位置:

当前位置: