基于FPGA的NoC验证平台的构建

[09-12 18:30:16] 来源:http://www.88dzw.com EDA/PLD 阅读:8321次

文章摘要:半导体工艺技术进入深亚微米时代后,基于总线系统芯片SoC(Svstem on Chip)的体系结构在物理设计、通信带宽以及功耗等方面无法满足未来多IP体系发展的需求。片上网络NoC(Netwotlk on Chip)是一种新的系统芯片体系结构,其核心思想是将计算机网络技术移植到系统芯片设计中来,从体系结构上彻底解决总线架构带来的问题。研究人员从拓扑结构、路由算法、交换策略以及流控机制等多个方面对NoC进行研究,但是如何构建NoC验证平台,快速得到NoC的性能也一直是NoC研究的重点。在过去的几年里,一些研究机构提出了对于NoC不同抽象层次的验证方法的研究,一般的NoC验证是基于软件的仿真和建模

基于FPGA的NoC验证平台的构建,标签:eda技术,eda技术实用教程,http://www.88dzw.com半导体工艺技术进入深亚微米时代后,基于总线系统芯片SoC(Svstem on Chip)的体系结构在物理设计、通信带宽以及功耗等方面无法满足未来多IP体系发展的需求。片上网络NoC(Netwotlk on Chip)是一种新的系统芯片体系结构,其核心思想是将计算机网络技术移植到系统芯片设计中来,从体系结构上彻底解决总线架构带来的问题。

研究人员从拓扑结构、路由算法、交换策略以及流控机制等多个方面对NoC进行研究,但是如何构建NoC验证平台,快速得到NoC的性能也一直是NoC研究的重点。

在过去的几年里,一些研究机构提出了对于NoC不同抽象层次的验证方法的研究,一般的NoC验证是基于软件的仿真和建模,如:用C、C++、SvstemC进行系统级建模仿真,这样验证很灵活,但在仿真时间上却开销很大。本文提出的基于FPGA的NoC验证平台在仿真速度方面是一般基于HDL的软件仿真的16 000倍,而基于PC机编写的NoC软件更增强了该平台的灵活性和实用性。

1 验证平台架构

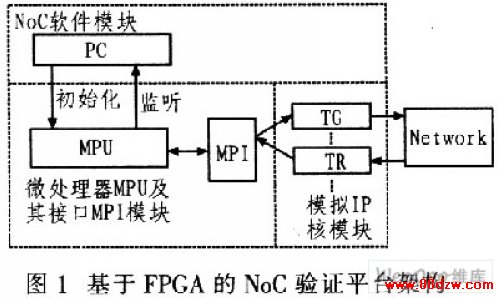

该验证平台采用模块化设计,可以很容易地对不同的NoC进行功能验证和性能*估。图1给出了该验证平台的基本架构。

它主要包括3个模块:

1)模拟IP核模块 该模块包含有数据流量产生器TG(Traffic Generator)模块及数据流量接收器TR(Traffic Receiver)模块。TG模拟产生NoC网络中各个IP节点可能产生的数据流量,TR用于收集NoC运行过程中的各种信息。TG/R作为一个IP节点和待测NoC中的每个交换节点相连接。

2)微处理器MPU及其接口MPI模块 PC机通过MPU(FPGA中自带的NiosⅡ软核)和MPI实现对NoC各IP核中TG内部各个配置寄存器的配置,并将TR中各个寄存器的内容读取到PC机中进行处理。本模块和模拟IP核模块构成FPGA硬件平台。

3)NoC软件模块 完成对NoC的配置以及NoC系统的性能统计。PC机通过MPU与FPGA进行通信,实现对NoC的配置并从FPGA中得到数据并进行后端处理,以图形的方式显示给用户,供用户对所设计的NoC进行*估。同时PC机可以监控NoC运行的情况。

FPGA采用Ahera公司Stratix IV系列中的EP4SGX230KF40C2,该器件能够提供高速的时钟信号和大量的片内资源,并具有大量外围接口电路可供使用,这为基于FPGA的验证提供了强有力的保证。

1.1 流量产生器TG

该平台中的TG是一个可重用的软核,用户可以通过为配置寄存器写入不同的配置信息使其产生不同的流量并注入NoC中。TR用于接收数据信息,并统计发包数和收包数。

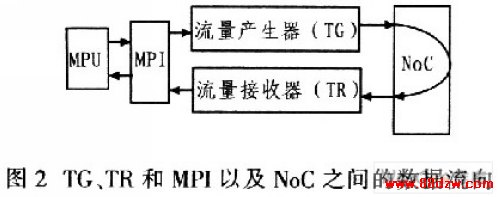

记录延时信息,统计误码个数。图2给出了TG、TR和MPI以及NoC之间的数据流向。

在片上网络中,流量的分布由以下2方面决定:1)流量的源/目的节点对的分布,即空间位置上的通信概率分布,称为空间分布;2)流量注入网络时,注入网络的时间间隔在时间上呈现的概率分布,称为时间分布。为了使该平台达到*价NoC性能的目的,流量产生器TG将从空间分布和时间分布的不同,模拟出不同的流量。

空间分布主要包括:1)给定目标地址:即配置TG产生发往确定目标地址的数据包;2)均匀分布:即配置TG产生均匀的发往网络中各个节点的数据包,类似于网络中的广播现象;3)热点分布:即配置TG产生发往网络中一些特定的数据交换相对频繁的节点的数据包;4)局部分布:即配置TG产生发往网络中某一局部的网络距离较近的节点的数据包;5)矩阵转换地址分布:即按照矩阵X,Y向量转置的特点。配置TG产生发往与发送节点地址相对应的节点的数据包。

时间分布主要包括:1)确定时间间隔:即配置TG每过一定数目的时钟周期发送1个数据包,直到停止发包为止;2)自相似流量模型:即ON-OFF流量模型。即配置TG在一段时间内发送数据包,在一段时间内停止发包。此类流量模型就是模拟现实中在某一段时间突发很大的流量,而在另外的时间段不产生流量;3)随机分布:即配置TG在发送1个数据包之间的间隔是1个随机时钟周期数。

《基于FPGA的NoC验证平台的构建》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的NoC验证平台的构建

- 在谷歌中搜索相关文章:基于FPGA的NoC验证平台的构建

- 在soso中搜索相关文章:基于FPGA的NoC验证平台的构建

- 在搜狗中搜索相关文章:基于FPGA的NoC验证平台的构建

当前位置:

当前位置: