基于FPGA的UART设计与实现

[09-12 18:35:16] 来源:http://www.88dzw.com EDA/PLD 阅读:8706次

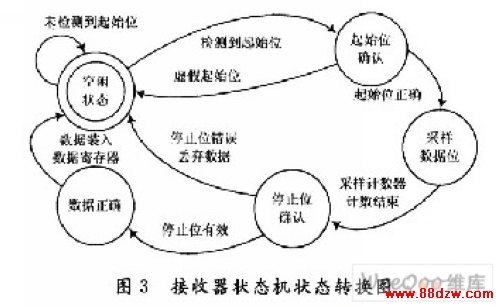

文章摘要:采用有限状态机模型可以更清晰明确地描述接收器的功能,便于代码实现。接收器的状态转换图如图3所示,为突出主要过程,图中省略了奇偶校验的情况。接收器状态机由5个工作状态组成,分别是空闲状态、起始位确认、采样数据位、停止位确认和数据正确,触发状态转换的事件和在各个状态执行的动作见图中的文字说明。在状态机模型的基础上,使用VHDL来描述接收器功能,其主要代码如下:实现用16倍波特率时钟确定起始位的具体方法是设计两个输入数据位寄存器rxd1和rxd2,使用语句“rxd1<=rxd;rxd2<=rxd1;”接收数据并进行判断。当检测到rxdl=O并且rxd2=1时可以确定下降沿发生,连续7个时

基于FPGA的UART设计与实现,标签:eda技术,eda技术实用教程,http://www.88dzw.com采用有限状态机模型可以更清晰明确地描述接收器的功能,便于代码实现。接收器的状态转换图如图3所示,为突出主要过程,图中省略了奇偶校验的情况。接收器状态机由5个工作状态组成,分别是空闲状态、起始位确认、采样数据位、停止位确认和数据正确,触发状态转换的事件和在各个状态执行的动作见图中的文字说明。

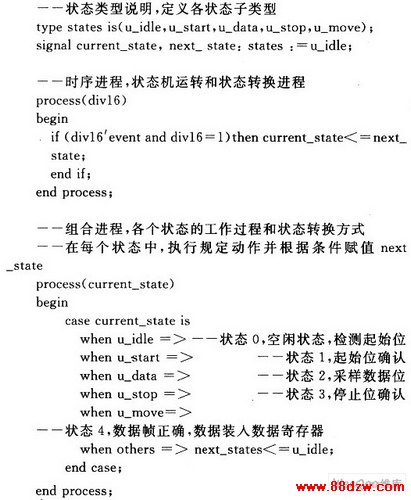

在状态机模型的基础上,使用VHDL来描述接收器功能,其主要代码如下:

实现用16倍波特率时钟确定起始位的具体方法是设计两个输入数据位寄存器rxd1和rxd2,使用语句“rxd1<=rxd;rxd2<=rxd1;”接收数据并进行判断。当检测到rxdl=O并且rxd2=1时可以确定下降沿发生,连续7个时钟rxd2=0即确定检测到起始位,之后为了确保在数据位中央接收数据,同样用16倍波特率时钟对数据位进行采样。接收数据的方法是设计一个寄存器rxd_buf(7 downto 0),用语句“rxd_buf(7)<=rxd2;rxd_buf(6 DOWNTO 0)<=rxd_buf(7 DOWNTO 1);”实现移位寄存器右移操作,执行8次后接收到一个完整数据。

1.3 波特率发生器设计

波特率发生器实质是设计一个分频器,用于产生和RS 232通信同步的时钟。在系统中用一个计数器来完成这个功能,分频系数N决定了波特率的数值。该计数器一般工作在一个频率较高的系统时钟下,当计数到N/2时将输出置为高电平,再计数到N/2的数值后将输出置为低电平,如此反复即可得到占空比50%的波特率时钟,具体的波特率依赖于所使用的系统时钟频率和N的大小。如系统时钟频率是40 MHz,要求波特率是9 600,则16倍波特率时钟的周期约等于260个系统时钟周期,则计数器取260/2=130时,当计数溢出时输出电平取反就可以得到16倍约定波特率的时钟。

使用VHDL来描述波特率发生器的完整代码如下:

2 数据传输测试

随着逻辑设计复杂性的不断增加,仅依赖于软件方式的仿真测试来了解系统的硬件功能有很多的局限性,应用QuartusⅡ集成开发环境中提供的SignalTapⅡ嵌入式逻辑分析仪,可以将测试信息随设计文件下载于目标芯片中,用以捕获目标芯片内部系统信号节点处的信息或总线上的数据流,而又不影响原硬件系统的正常工作。测试信息通过器件的JTAG端口传出,并送入计算机进行显示和分析,这是一种高效的硬件测试手段,并很好地结合了传统的系统测试方法。

本设计在Altera Cyclone系列的EPlC6Q240C8芯片上进行了验证,使用QuarltusⅡ软件将编译好的.pof格式文件以AS模式下载到配置芯片EPCS1中。在计算机端运行串口调试助手软件,将数据从计算机送出,并利用FPGA上的UART模块进行接收,将发送数据与SignalTapⅡ获取的波形进行对比,经多次测试表明收发数据完全相同。

以其中一次的测试为例进行说明,从PC上输入ASCII码的“6”,设定波特率发生器时钟作为SignalTapⅡ的采样时钟,采样波形如图4所示,其中“recstart”表示开始接收数据帧标志;“divl6”表示16倍波特率时钟;“cnt_rxd”表示数据位采样计数器,一次完整的采样计数从Oh~9h共10次采样(1个起始位,8个数据位,1个停止位);“rxd”表示串口的接收端;“rxd_buf”表示移位寄存器,当数据停止位确认后,移位寄存器输出收到的数据“36h”,表明了该UART工作稳定可靠。

《基于FPGA的UART设计与实现》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的UART设计与实现

- 在谷歌中搜索相关文章:基于FPGA的UART设计与实现

- 在soso中搜索相关文章:基于FPGA的UART设计与实现

- 在搜狗中搜索相关文章:基于FPGA的UART设计与实现

当前位置:

当前位置: