在修改BiCMOS工艺条件下实现光电集成

[11-20 00:52:58] 来源:http://www.88dzw.com 集成电路 阅读:8137次

文章摘要:图2 利用SiGe作应变缓冲层的锗探测器以上介绍的几种SiGe探测器都是分立的,虽然它们的制作工艺大都和微电子工艺兼容。SiGe/Si技术的发展使得异质结晶体管成为现实,这种双异质结构晶体管(HBT)可以获得很好的注入比和很高的本征频率,如果能将SiGe探测器和HBT放大电路集成在同一衬底上则可大大提高0EIC速度[81〕,如图3所示。PIN-HBT结构通过一步分子速外延而成。表1是各个层组分和掺杂特性,发射极和集电极是掺Sb的Si,基极是窄禁带宽度的SiGe,锗组分的含量从发射极这一侧的0.1渐变到集电极一侧的0.4。这样的渐变层能在基极形成“准”电场(Quasi-Electric Fi

在修改BiCMOS工艺条件下实现光电集成,标签:集成电路设计,半导体集成电路,http://www.88dzw.com

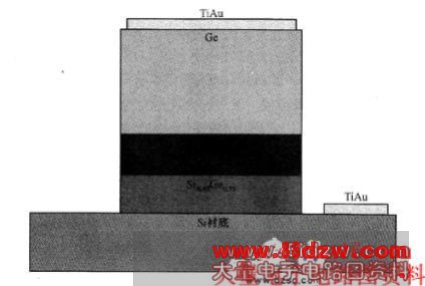

图2 利用SiGe作应变缓冲层的锗探测器

以上介绍的几种SiGe探测器都是分立的,虽然它们的制作工艺大都和微电子工艺兼容。SiGe/Si技术的发展使得异质结晶体管成为现实,这种双异质结构晶体管(HBT)可以获得很好的注入比和很高的本征频率,如果能将SiGe探测器和HBT放大电路集成在同一衬底上则可大大提高0EIC速度[81〕,如图3所示。PIN-HBT结构通过一步分子速外延而成。表1是各个层组分和掺杂特性,发射极和集电极是掺Sb的Si,基极是窄禁带宽度的SiGe,锗组分的含量从发射极这一侧的0.1渐变到集电极一侧的0.4。这样的渐变层能在基极形成“准”电场(Quasi-Electric Field)来加速电子在基区的输运过程。PIN则由N+-集电极和p+-SiGe构成,N-集电极作为PIN的本征吸收区。整个器件被台面结构隔离,PIN台面二极管面积为12 gm×13 gm。在外延生长过后,发射极接触被用电子束蒸发方法得到,接着用SF6/02干法刻蚀和KOH湿法刻蚀得到发射极台面结构。基区和集电区台面结构用干法刻蚀即可形成。最后用等离子增强化学气相淀积法淀积一层SiO,。在4 V和9 V的反向偏压下,二极管的暗电流为0.1uA和1uA°对于850 nm波长入射光和9 V反向偏压下,测得带宽为450 MHz1.1 gm厚的SiO,作为抗反射层使得在5V偏压下响应度为0.3 AIW,响应量子效率为43%。由于本征吸收层还是51层,因此p+-SiGe阳极并没有将量子效率提高太多。为了提高响应度和波长响应有必要增加本征区锗含量,然而这会增加暗电流。可以通过生长多层SiGe/Si超晶格结构在增强本征区吸收的同时,将暗电流减小到较低水平。

图3 PIN-HBT横截面结构图

表1 PIN-HBT各层组分和掺杂浓度

欢迎转载,信息来自www.88dzw.com(www.88dzw.com)

《在修改BiCMOS工艺条件下实现光电集成》相关文章

- › 在修改BiCMOS工艺条件下实现光电集成

- 在百度中搜索相关文章:在修改BiCMOS工艺条件下实现光电集成

- 在谷歌中搜索相关文章:在修改BiCMOS工艺条件下实现光电集成

- 在soso中搜索相关文章:在修改BiCMOS工艺条件下实现光电集成

- 在搜狗中搜索相关文章:在修改BiCMOS工艺条件下实现光电集成

当前位置:

当前位置: