中规模时逻辑集成计数器

[11-20 00:54:32] 来源:http://www.88dzw.com 集成电路 阅读:8870次

文章摘要:在数字电路中,把记忆输人脉冲个数的操作称为计数,计数器就是实现计数操作的时序逻辑电路。计数 器应用非常广泛,除用于计数、分频外,还用于数字测量、运算和控制,从小型数字仪表到大型数字电子 计算机,几乎无所不在,是任何现代数字系统中不可缺少的组成部分。计数器的种类很多,按其进制不同分为二进制计数器、十进制计数器、N进制计数器;按触发器翻转是否 同步分为异步计数器和同步计数器;按计数时是增还是减分为加法计数器、减法计数器和加/减法(可逆 )计数器。下面首先介绍二进制计数器。1.集成二进制计数器74LS16174LS161是4位二进制同步加法计数器,除了有二进制加法计数功能外,还具有异步清零、同步并行

中规模时逻辑集成计数器,标签:集成电路设计,半导体集成电路,http://www.88dzw.com在数字电路中,把记忆输人脉冲个数的操作称为计数,计数器就是实现计数操作的时序逻辑电路。计数 器应用非常广泛,除用于计数、分频外,还用于数字测量、运算和控制,从小型数字仪表到大型数字电子 计算机,几乎无所不在,是任何现代数字系统中不可缺少的组成部分。

计数器的种类很多,按其进制不同分为二进制计数器、十进制计数器、N进制计数器;按触发器翻转是否 同步分为异步计数器和同步计数器;按计数时是增还是减分为加法计数器、减法计数器和加/减法(可逆 )计数器。下面首先介绍二进制计数器。

1.集成二进制计数器74LS161

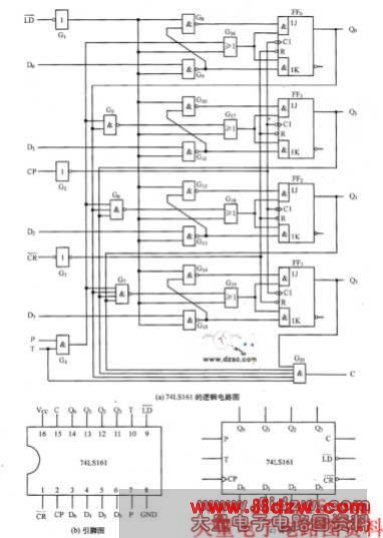

74LS161是4位二进制同步加法计数器,除了有二进制加法计数功能外,还具有异步清零、同步并行置数 、保持等功能。74LS161的逻辑电路图和引脚排列图如图1所示,CR是异步清零端,LD是预置数控制端,D0 ,D1,D2,D3是预置数据输人端,P和T是计数使能端,C是进位输出端,它的设置为多片集成计数器的级 联提供了方便。

74LS161的功能表如表1所示。由表可知,74LS161具有以下功能。

图1 74LSl61的逻辑电路图和引脚图

(1)异步清零功能

当CR=0时,不管其他输人端的状态如何(包括时钟信号CP),4个触发器的输出全为零。

(2)同步并行预置数功能

在CR=1的条件下,当LD=0且有时钟脉冲CP的上升沿作用时,D3,D2,D1,D0输入端的数据将分别被Q3~Q0所接收。由于置数操作必须有CP脉冲上升沿相配合,故称为同步置数。

(3)保持功能

在CR=LD=1的条件下,当T=P=0时,不管有无CP脉冲作用,计数器都将保持原有状态不变(停止计数) 。

(4)同步二进制计数功能

当CR=LD=P=T=1时,74LS161处于计数状态,电路从0000状态开始,连续输入16个计数脉冲后,电路 将从1111状态返回到0000状态,状态表见表2。

(5)进位输出C

当计数控制端T=1,且触发器全为1时,进位输出为1,否则为零。

表1 74LS161的功能表

表2 进制同步加法计数器的状态表

若输入计数器的CP脉冲频率为f,则从Qo端输出脉冲频率为f/2,通常也称Qo端输出信号是输人计数脉冲 CP的2分频信号,Q1端输出信号是输人计数脉冲CP的4分频信号,Q4端输出信号是输人计数脉冲CP的16分频 信号。N进制计数器可实现n分频。

2.十进制计薮器

二进制计数器电路简单,运算也方便,但人们最习惯的是十进制,所以在应用中常使用十进制计数器。使用较多的十进制计数器是按照8421BCD码进行计数的电路,计数器由“0000”状态开始计 数,每10个脉冲一个循环,也就是第10个脉冲到来时,由“1001”变为“0000”,就实现了“逢十进一” ,同时产生一个进位信号。74LS160是集成同步十进制计数器,它是按8421BCD码进行加法计数的, 74LS160的引脚图、逻辑功能与74LS161相同,只是计数状态是按照十进制加法规律来计数的,因此不再重 述。

3.利用集成计数器构成Ⅳ进制计数器

目前集成计数器的品种很多,功能完善,通用性强,在实际应用中,如果要设计各种进制的计数器,可 以直接选用集成计数器,外加适当的电路连接而成。在使用集成计数器时,不必去剖析集成电路的内部结 构,一般只需查阅手册给出的功能表和芯片引脚,按其指定的功能使用即可。

- 上一篇:中规模时逻辑集成移位寄存器

《中规模时逻辑集成计数器》相关文章

- › 中规模时逻辑集成计数器

- › 中规模时逻辑集成移位寄存器

- 在百度中搜索相关文章:中规模时逻辑集成计数器

- 在谷歌中搜索相关文章:中规模时逻辑集成计数器

- 在soso中搜索相关文章:中规模时逻辑集成计数器

- 在搜狗中搜索相关文章:中规模时逻辑集成计数器

当前位置:

当前位置: