基于FPGA的NAND Flash ECC校验

[10-10 20:38:44] 来源:http://www.88dzw.com 其它电路 阅读:8200次

文章摘要: 对于1 bit错误的情况,出错地址可通过将原有ECCo值和新ECCo值进行按位“异或”来识别获取。通过图5中的计算,结果为2,表明原数据第2 bit位出现了问题。该计算采用奇校验数据ECCo,这是因为它们可以直接地反映出出错比特的位置。 找到出错比特后,只要通过翻转它的状态就可修复数据包,具体操作也就是将该位与“1”进行异或操作,如图6所示。2 扩展数据包 在上述举例中,校验1个8 bit数据包需要6 bit的ECC数据。在这种情况下,校验数据量达到原始数据包的数据量的75%,看上去并不令人满意。然而,随着数据包大小的增加,H

基于FPGA的NAND Flash ECC校验,标签:电路设计,http://www.88dzw.com

对于1 bit错误的情况,出错地址可通过将原有ECCo值和新ECCo值进行按位“异或”来识别获取。通过图5中的计算,结果为2,表明原数据第2 bit位出现了问题。该计算采用奇校验数据ECCo,这是因为它们可以直接地反映出出错比特的位置。

![]()

找到出错比特后,只要通过翻转它的状态就可修复数据包,具体操作也就是将该位与“1”进行异或操作,如图6所示。

![]()

2 扩展数据包

在上述举例中,校验1个8 bit数据包需要6 bit的ECC数据。在这种情况下,校验数据量达到原始数据包的数据量的75%,看上去并不令人满意。然而,随着数据包大小的增加,Hamming算法将表现得越来越有效率。由前面2n bit数据需要2n bit ECC校验的关系推知,每增加一倍的数据要求两个额外的ECC信息比特。这样,当数据增加到,比如512 Byte时,仅产生24 bit的ECC,此时用于校验的数据占原数据的比例降为0.06%,效率较高。下面,以1个8 Byte的数据包为例说明扩展数据包的校验情况。

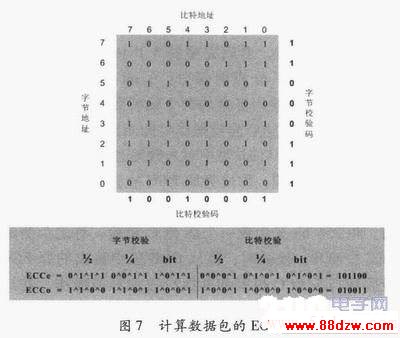

在这里,由于异或操作满足交换律,用一种更为有效的方法进行校验。如图7所示,首先将该8 Byte数据排为1个矩阵的形式,每行为1B-yte。分别计算每行各bit的异或结果记为字节校验码(Byte-Wise),计算每列各bit的异或结果记为比特校验码(Bit-Wise)。接下来,将两个校验码分别按上述方法分割计算得到ECC校验码,并将字节校验码的ECC结果作为ECCe和ECCo的高有效位(MSB)、比特校验码的ECC结果做为低有效位(LSB)进行组合,最终得到8 Byte数据包的ECC校验码。

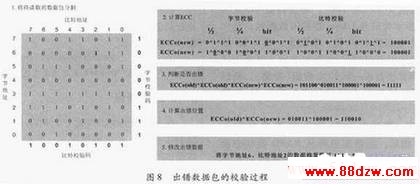

当数据包发生错误时,错误检测和更正所使用的方法与先前所描述的方法相似,这里仍以1 bit错误来说明校验过程,具体如图8所示。

经步骤1~步骤4的计算,新的数据包存在错误且出错位置为“110010”,由于前面将字节校验码设为ECC值的高位,比特校验码设为低位,因此,“110010”的高有效位表示出错的字节地址,低有效位代表出错的比特地址,即字节地址为6、比特地址为2的数据发生了错误,与设定的错误情况相符。此时,只需将该位的数据比特与“1”异或即可完成数据包的修正。

将8 Byte数据包扩展到512 Byte数据包,虽然数据量大大增加,但仅添加了数据分割的情况,算法仍然一样。计算所得奇偶ECC数据均为12 bit长,其中,3个低有效位代表bit地址(7~0),9个高有效位代表512Byte的地址(255~0)。

- 上一篇:光伏并网发电模拟装置研制

《基于FPGA的NAND Flash ECC校验》相关文章

- › 基于FPGA的1553B通信模块的设计

- › 基于FPGA的工控领域监控系统设计

- › 基于FPGA的嵌入式系统USB接口设计

- › 基于FPGA的NAND Flash ECC校验

- › 基于FPGA的实时中值滤波器硬件实现

- › 一种基于FPGA控制全彩大屏幕显示的设计

- 在百度中搜索相关文章:基于FPGA的NAND Flash ECC校验

- 在谷歌中搜索相关文章:基于FPGA的NAND Flash ECC校验

- 在soso中搜索相关文章:基于FPGA的NAND Flash ECC校验

- 在搜狗中搜索相关文章:基于FPGA的NAND Flash ECC校验

当前位置:

当前位置: