基于FPGA的NAND Flash ECC校验

[10-10 20:38:44] 来源:http://www.88dzw.com 其它电路 阅读:8200次

文章摘要:3 实验分析 本实验处理对像为256 Byte的数据包,对其进行ECC校验共生成22 bit校验数据。为方便读取,可以在末尾添加两位,形成完整的3Byte校验数据。这3 Byte共24 bit,分成两部分:6 bit的比特校验和16 bit的字节校验,多余的两个比特置1并置于校验码的最低位,在进行异或操作时此两比特忽略。 当往NAND Flash页中写人数据时,每256 bit生成一个ECC校验,称之为原ECC校验和,并保存到页的OOB数据区中;当从NAND Flash中读取数据的时,每256 bit又生成一个新ECC校验,称之为新的ECC校验和。校验时,将从OOB区中读出的原EC

基于FPGA的NAND Flash ECC校验,标签:电路设计,http://www.88dzw.com3 实验分析

本实验处理对像为256 Byte的数据包,对其进行ECC校验共生成22 bit校验数据。为方便读取,可以在末尾添加两位,形成完整的3Byte校验数据。这3 Byte共24 bit,分成两部分:6 bit的比特校验和16 bit的字节校验,多余的两个比特置1并置于校验码的最低位,在进行异或操作时此两比特忽略。

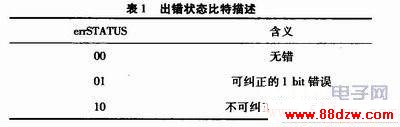

当往NAND Flash页中写人数据时,每256 bit生成一个ECC校验,称之为原ECC校验和,并保存到页的OOB数据区中;当从NAND Flash中读取数据的时,每256 bit又生成一个新ECC校验,称之为新的ECC校验和。校验时,将从OOB区中读出的原ECC校验和与新ECC校验和并执行按位异或操作,若计算结果为全“0”,则表示不存在出错,并将出错状态变量errSTATUS赋值为“00”;若结果为全“1”,表示出现1个比特错误,将errSTATUS赋值为"01”并进行纠正;除全“0”和全“1”外的其他情况将errSTATUS赋值为“10”表示出现了无法纠正的2 bit错误,如表1所示。

实验仿真环境为ALTEra Quartus II 7.0,编程语言为VHDL。VHDL语言为硬件编程语言,具有并行处理的特点,而原程序中有大量的需要并行处理的异或操作,因此程序执行效率高,非常有利于硬件实现。

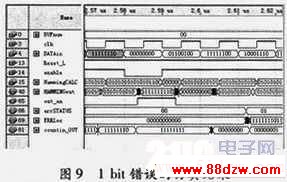

图9给出了数据包发生1 bit错误的校验情况。其中,DATAin表示待读取的数据,HammingCALC表示在写入NAND Flash页时计算好的原始ECC,HAMMINGout表示后面在读取DATAin数据时计算的新的ECC,errSTATUS为出错状态,ERRIoc为计算所得出错的位置。为满足1 bit错误的条件且易于观察,将256 Byte数据(0~255)的最后一个Byte由“11110110”变为“11111110”,如图9中阴影部分所示。此时,errSTATUS结果为"01”,表明程序检测出了该1 bit错误,且ERRLOC输出为“111111111O11”,即出错位置为第255 Byte的比特3发生了错误。为纠正该错误,此时,只要将该位置的比特取反输出即可。

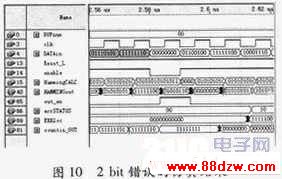

在原来1 bit错误的情况下,将其相邻的第254 bit的数据由“11110101”变为“01110101”,如图10阴影部分所示,整个数据包有2 bit发生了变化。此时,errSTATUS结果显示为“10”,即检测出了有2 bit错误。但此时的ERRloe无效,不能表征出两个出错的位置,也就是为什么ECC校验只能检测出2 bit错误而不能对其进行更正的原因。

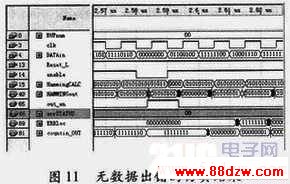

当然,如果数据包没有发生任何错误,也就是若读出的数据与先前写入的数据完全一致,ECC校验也是能够保证检测出来的。如图11所示,当未发生任何错误时,errSTATUS为“00”,验证了数据的一致性。此时,ERPloe无意义。

Tag:其它电路,电路设计,家电维修 - 单元电路介绍 - 其它电路

- 上一篇:光伏并网发电模拟装置研制

《基于FPGA的NAND Flash ECC校验》相关文章

- › 基于FPGA的1553B通信模块的设计

- › 基于FPGA的工控领域监控系统设计

- › 基于FPGA的嵌入式系统USB接口设计

- › 基于FPGA的NAND Flash ECC校验

- › 基于FPGA的实时中值滤波器硬件实现

- › 一种基于FPGA控制全彩大屏幕显示的设计

- 在百度中搜索相关文章:基于FPGA的NAND Flash ECC校验

- 在谷歌中搜索相关文章:基于FPGA的NAND Flash ECC校验

- 在soso中搜索相关文章:基于FPGA的NAND Flash ECC校验

- 在搜狗中搜索相关文章:基于FPGA的NAND Flash ECC校验

最新更新

当前位置:

当前位置: