低频数字相位(频率)测量的CPLD实现

[09-12 18:25:52] 来源:http://www.88dzw.com EDA/PLD 阅读:8477次

文章摘要:在电子测量技术中,测频测相是最基本的测量之一。相位测量仪是电子领域的常用仪器,当前测频测相主要是运用等精度测频、PLL锁相环测相的方法。研究发现,等精度测频法具有在整个测频范围内保持恒定的高精度的特点,但是该原理不能用于测量相位。PLL锁相环测相可以实现等精度测相,但电路调试较复杂。因此,选择直接测相法作为低频测相仪的测试方法。设计的低频测相仪,满足以下的技术指标:a .频率20-20KHz;b .输入阻抗≥100KΩ;c.相位测量绝对误差≤1度; d.具有频率测量和数字显示功能;e.显示相位读数为0度--359度。1系统工作原理图1 测频测相系统原理框图系统工作原理如图1所示,系统运行时,首

低频数字相位(频率)测量的CPLD实现,标签:eda技术,eda技术实用教程,http://www.88dzw.com在电子测量技术中,测频测相是最基本的测量之一。相位测量仪是电子领域的常用仪器,当前测频测相主要是运用等精度测频、PLL锁相环测相的方法。研究发现,等精度测频法具有在整个测频范围内保持恒定的高精度的特点,但是该原理不能用于测量相位。PLL锁相环测相可以实现等精度测相,但电路调试较复杂。因此,选择直接测相法作为低频测相仪的测试方法。

设计的低频测相仪,满足以下的技术指标:a .频率20-20KHz;b .输入阻抗≥100KΩ;c.相位测量绝对误差≤1度; d.具有频率测量和数字显示功能;e.显示相位读数为0度--359度。

1系统工作原理

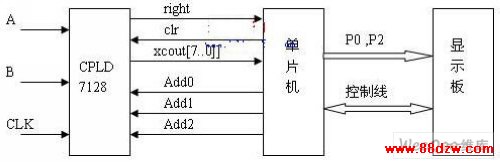

图1 测频测相系统原理框图

系统工作原理如图1所示,系统运行时,首先由单片机通过clr控制线送清零信号,启动CPLD的计数模块,在设计的CPLD内部控制模块作用下,记录AB两相的相差间隔时间内的标频个数(测相计数器),同时也记录下A相一个周期内的标频个数(测频计数器),此后测频和测相计数器处于保持状态,同时送出right信号表明完成测频测相的计数,单片机可以读数据。

单片机和CPLD的数据采用独立接口方式,这样设计比较灵活,可以不受单片机总线时序的影响。由ADD[0..2]进行控制,分别读取测频测相计数器中的19位数据,并存于单片机中,进行后续的计算。单片机完成数据的运算后,将所得数据转化为10进制,送到显示板进行显示。显示板共有8个数码管,其中,前5位用于显示频率(最大为20000Hz),后三位显示相位(最大为359度)。

在CPLD设计中,根据计算,选取测频、测相计数器长度均为19位,在标频信号为10MHz时,相位测量精度小于1度。若只用89C51,其自带的计数器只有16位,且不易同时实现测频测相的功能。故选用CPLD实现其测频测相的计数功能,并设计了独立的数据接口,以便与单片机交换数据。

2 CPLD测频测相模块工作原理

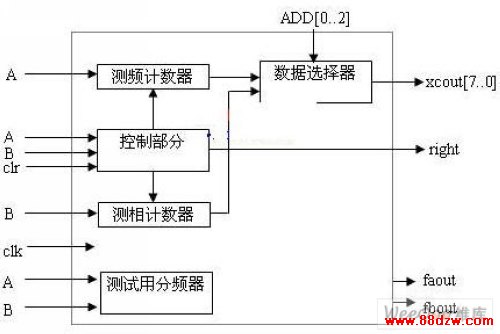

图2 CPLD测频测相内部原理框图

如图2所示,利用VHDL语言设计了完成测频测相计数功能的数字芯片。整个芯片由测频计数器、测相计数器、控制部分、数据选择器和测试用分频器5个部分组成。

控制部分主要是利用状态机原理,设计了检测一个测频周期的控制电路。在clr信号为高时,启动测频测相计数器,此时,状态机处于计数工作状态;当A相第一个上升沿到来时,测频测相计数器同时启动,开始计数;当B相第一个上升沿到来时,控制部分控制测相计数器停止计数;当A相第二个上升沿到来时,控制部分控制测频计数器停止计数,同时送出计数完成信号right;此后测频测相计数器处于保持状态。

单片机读数时,通过设置add[0..2]数据选择器的地址选通端,依次送出测频计数器中的19位数据,8位一组,从xcout[0..7]端口送出,单片机需分3次读完测频计数器中的19位数据,数据选通端设置为001,010,011;同理,单片机也需分3次读完测相计数器中的19位数据,数据选通端设置为100,101,110。

为了测试方便,设计了测试用分频器,该分频器系数可以在VHDL源程序中改动,如为1000,则将测试时用的标频信号10M进行1000分频,分频后频率为10KHz,正好处于20-20KHz范围内。

3 单片机程序

如图3所示,系统上电后,首先由单片机送出清零信号,启动CPLD中的测频测相计数器,CPLD进行测频测相的计数,单片机查询到right=1,则表明计数器完成计数工作,开始读取CPLD中的数据。否则,就等待。单片机通过控制CPLD中数据选择器的地址选通端add[0..7],分别读取测频、测相计数器的19位数据,并进行相应的计算。计算中首先调用频率计算子程序,计算出相应的频率,然后再调用相位计算子程序,计算出相应的相位,再调用进制转换程序,将16进制的数转换成10进制,最后调用显示子程需,在8位数码管中显示出测量的频率、相位值。由于篇幅关系,此处不再详述具体程序和显示部分的设计。

《低频数字相位(频率)测量的CPLD实现》相关文章

- › 低频数字相位(频率)测量的CPLD实现

- › 基于单片机的低频数字相位测量仪的设计

- 在百度中搜索相关文章:低频数字相位(频率)测量的CPLD实现

- 在谷歌中搜索相关文章:低频数字相位(频率)测量的CPLD实现

- 在soso中搜索相关文章:低频数字相位(频率)测量的CPLD实现

- 在搜狗中搜索相关文章:低频数字相位(频率)测量的CPLD实现

当前位置:

当前位置: