利用FPGA实现HDB3编解码功能

[09-12 18:27:49] 来源:http://www.88dzw.com EDA/PLD 阅读:8782次

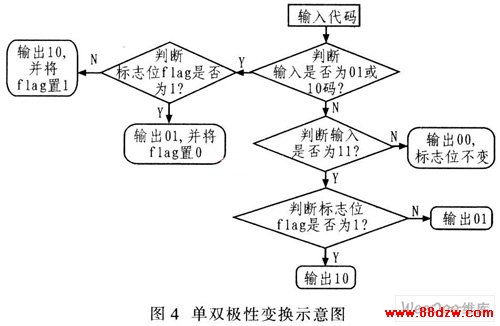

文章摘要:2.3 单双极性变换过程分析HDB3码的编码规则,发现V码的极性是正负交替的,余下的“1”和B码的极性也是正负交替的,且V码的极性与V码之前的非零码极性一致。因此可以将所有的“1”和B码取出来做正负交替变换,而V码的极性则根据“V码的极性与V码之前的非零码极性一致”这一特点进行正负交替变换。具体操作是设置一个标志位flag,通过检测判断标志位的状态来确定是否进行单双极性变换,标志位要交替变换以实现“l”和“B”正负交替,V码的极性也根据标志位变换。图4是单双极性变换过程的流程,“10”表示输出正电平,“Ol”表示输出负电平,“00”表示输出为零电平。3 HDB3解码模块设计根据编码规则,V码是

利用FPGA实现HDB3编解码功能,标签:eda技术,eda技术实用教程,http://www.88dzw.com

2.3 单双极性变换过程

分析HDB3码的编码规则,发现V码的极性是正负交替的,余下的“1”和B码的极性也是正负交替的,且V码的极性与V码之前的非零码极性一致。因此可以将所有的“1”和B码取出来做正负交替变换,而V码的极性则根据“V码的极性与V码之前的非零码极性一致”这一特点进行正负交替变换。具体操作是设置一个标志位flag,通过检测判断标志位的状态来确定是否进行单双极性变换,标志位要交替变换以实现“l”和“B”正负交替,V码的极性也根据标志位变换。图4是单双极性变换过程的流程,“10”表示输出正电平,“Ol”表示输出负电平,“00”表示输出为零电平。

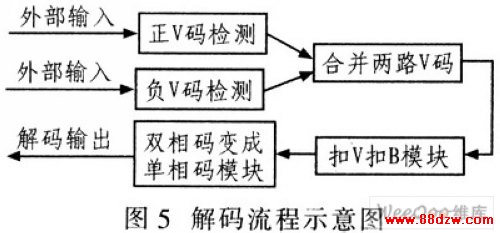

3 HDB3解码模块设计

根据编码规则,V码是为了解决4连零现象而插入的,而B码总是出现在V码之前,且只相隔2个“0”,因此只要在接收到的信号中找到V码并将其和前面的3位代码全部复原成“0”即可完成解码过程。

3.1 HDB3解码模块建模

首先外围电路从HDB3码中提取出时钟、正整流信号和负整流信号,将这3路信号送到FPGA中,解码模块所用的时钟是从HDB3码中提取出来的时钟。从正整流信号和负整流信号中可以检测出2路包含V码的信号,将2路V码合成一路信号,然后对该路信号进行解码,最后将双相码变成单相码,图5是解码过程的流程。

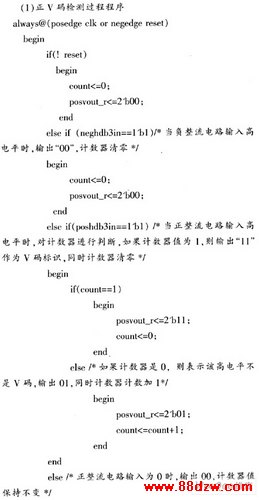

3.1.1 V码检测过程

V码检测同时进行正V码检测和负V码检测,这两个检测模块的设计思想类似,这里对正V码检测模块进行详细说明。为了方便描述,假设从正整流电路输入的信号为+P,从负整流电路输入的信号为-N。+V码检测模块是在-N的控制下,对输入的+P进行检测。其原理是:当+P的上升沿到来时,对输入的+P脉冲进行计数,当计数到1时,输出一个脉冲作为+V脉冲,同时计数器清零,在计数期间,一旦检测到-N信号脉冲,计数器立即清零,计数器重新从零计数。这是因为在两个+P脉冲之间,存在-N脉冲,说明第2个+P脉冲不是+V码,只有在连续两个+P脉冲之间无-N脉冲,才能说明这两个P脉冲在HDB3码中是真正同极性的,才可以判断第2个P脉冲实际上是+V码,达到检测+V码的目的。-V码检测原理与+V码检测类似,所不同的是,-V码检测电路是在+P控制下,对-N信号进行计数、检测和判定。

3.1.2 V码和B码解码过程

检测V码后,根据HDB3编码规则,只需将V码及之前3位码全部置零就可同时完成扣V/扣B操作。这又会涉及到一个由现在事件状态决定过去事件状态的情况,仍可采用两组4位移位寄存器解决。根据编码规则,V码是取代连“0”串中的第4个“0”,而B码总是出现在V码之前,且只相隔两个“O”,当输入是V码后,只需同时将4位移位寄存器置零,即可同时完成V码和B码的解码过程。扣除V码和B码后,还需将双相码变换成单相码,即当输入是“00”时输出“0”,输入是“01”时输出“l”,至此便完成了HDB3解码。

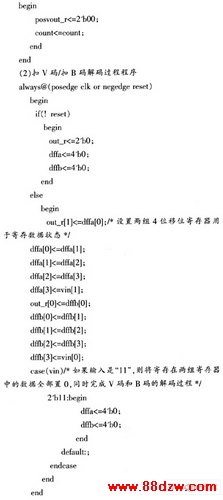

3.2 HDB3解码的Verilog HDL实现

以下利用硬件描述语言实现解码功能,这里只给出正V码检测模块和扣V码/扣B码模块的关键程序。

《利用FPGA实现HDB3编解码功能》相关文章

- › 利用FPGA协处理器提升无线子系统的性能

- › 利用FPGA协处理提升无线子系统性能

- › 利用FPGA实现视频监控系统的视频处理

- › 利用FPGA实现低成本汽车多总线桥接

- › 利用FPGA和CPLD数字逻辑实现ADC

- › 利用FPGA实现高性能数字电视系统

- 在百度中搜索相关文章:利用FPGA实现HDB3编解码功能

- 在谷歌中搜索相关文章:利用FPGA实现HDB3编解码功能

- 在soso中搜索相关文章:利用FPGA实现HDB3编解码功能

- 在搜狗中搜索相关文章:利用FPGA实现HDB3编解码功能

当前位置:

当前位置: