在FPGA中实现源同步LVDS接收正确字对齐

[09-12 18:28:51] 来源:http://www.88dzw.com EDA/PLD 阅读:8930次

文章摘要:与这类单独的LVDS SERDES器件相比,FPGA集成LVDS模块能提供更高的集成度,并简化硬件设计、节省PCB面积,从而降低应用成本。高端FPGA还在I/O单元里固化了LVDS串行器/解串器,支持非常高的速率,比如Altera公司的Stratix III系列。Stratix III FPGA系列是Altera公司基于TSMC 65nm工艺的高端FPGA,是业界高密度高性能可编程逻辑器件中,功耗最低的产品系列。Stratix III 器件可以同时提供最多276对LVDS串行化发送模块和276对LVDS解串行化接收模块,每路LVDS最高可以支持1.6Gbps。此外,它还独家提供可编程的输出摆幅

在FPGA中实现源同步LVDS接收正确字对齐,标签:eda技术,eda技术实用教程,http://www.88dzw.com与这类单独的LVDS SERDES器件相比,FPGA集成LVDS模块能提供更高的集成度,并简化硬件设计、节省PCB面积,从而降低应用成本。高端FPGA还在I/O单元里固化了LVDS串行器/解串器,支持非常高的速率,比如Altera公司的Stratix III系列。

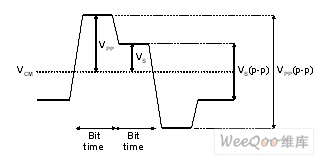

Stratix III FPGA系列是Altera公司基于TSMC 65nm工艺的高端FPGA,是业界高密度高性能可编程逻辑器件中,功耗最低的产品系列。Stratix III 器件可以同时提供最多276对LVDS串行化发送模块和276对LVDS解串行化接收模块,每路LVDS最高可以支持1.6Gbps。此外,它还独家提供可编程的输出摆幅和预加重功能,以支持长距离背板传送,如图4所示。

图4:Stratix III 支持可编程的输出摆幅(Vs(p-p))和预加重(Vpp(p-p))。

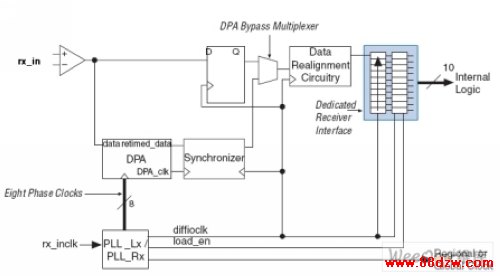

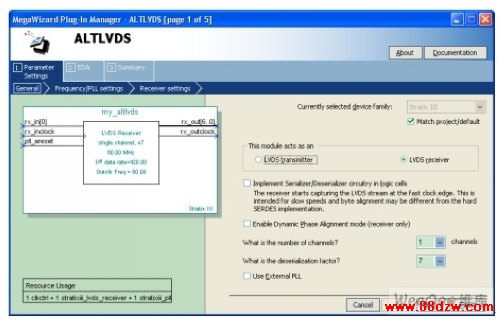

图5显示了Stratix III的LVDS接收器中固化在I/O单元里的模块。源同步的低频时钟rx_inclk通过PLL倍频移相后得到DIFFI/OCLK,对输入数据rx_in进行采样,采样后的数据可以进行最高因子为10的解串行化。

图5:Stratix III I/O固化的LVDS接收器。

由于FPGA具有非常高的灵活性,比如支持不同LVDS输入数据和输入时钟之间的倍频关系,以及不同的解串行化因子,所以Stratix III LVDS硬核模块的输出字顺序通常是不确定的,每次上电或者复位后字顺序都有可能发生变化,使用时需要根据特殊码型进行字对齐处理。

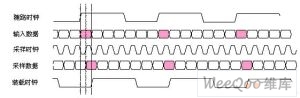

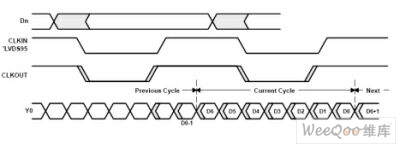

当输入到FPGA的数据和时钟之间的倍数关系等于解串器的解串行化因子时,FPGA与单独的LVDS解串器一样,有确定的字顺序输出,可以在没有训练码型的情况下继续正常应用。图6是解串行化因子为7时的时序图。假设随路时钟的上升沿对应数据的最高比特,在FPGA内部,PLL会从随路时钟产生一个进行过相位调整的7倍频率采样时钟。此时钟对输入数据进行采样后送入解串器,通过控制解串器的装载时钟相位,得到确定的并行数据输出字顺序。装载时钟的相位相对随路时钟相位的固定差异是通过接收PLL的相位控制来实现的,因此必须在输入时钟稳定后再释放PLL的复位控制,或者等输入时钟稳定后再复位PLL一次,否则输出的字顺序在每次上电时都可能不固定。

图6:LVDS接收及解串行化时序图。

在具体应用时,还需通过仿真来确定具体应用下的字输出顺序,然后在逻辑设计里面进行调整,使最终的并行输出符合满足需求。下面以与TI的SN65LVDS95 LVDS发送器对接为例来介绍具体的设计方法和步骤。当把Stratix III的LVDS与别的LVDS器件对接时,也可以此为参考。

图7:LVDS95输出时序。

在图7,LVDS95输出的时钟和数据是对齐到输出时钟的上升沿上的,数据的最高比特(MSB)出现在时钟上升沿之在后的第三个比特。这里的目的是使Stratix III 的LVDS接收器输出正确的字顺序,也即图7中的D6出现在并行输出数据的最高比特上。

《在FPGA中实现源同步LVDS接收正确字对齐》相关文章

- › 在FPGA中实现PCI Express桥接解决方案

- › 在FPGA中实施4G无线球形检测器

- › 在FPGA中实现源同步LVDS接收正确字对齐

- › 雷达视频积累算法在FPGA上的实现

- › CVSD算法分析及其在FPGA中的实现

- › IIR数字滤波器设计-在FPGA上实现任意阶IIR数字滤波器

- 在百度中搜索相关文章:在FPGA中实现源同步LVDS接收正确字对齐

- 在谷歌中搜索相关文章:在FPGA中实现源同步LVDS接收正确字对齐

- 在soso中搜索相关文章:在FPGA中实现源同步LVDS接收正确字对齐

- 在搜狗中搜索相关文章:在FPGA中实现源同步LVDS接收正确字对齐

当前位置:

当前位置: