在FPGA中实现源同步LVDS接收正确字对齐

[09-12 18:28:51] 来源:http://www.88dzw.com EDA/PLD 阅读:8930次

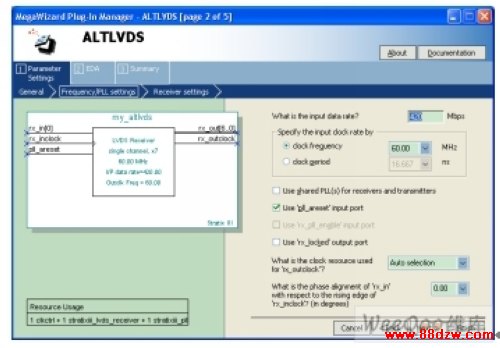

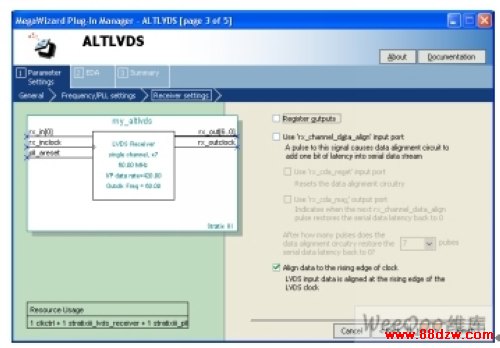

文章摘要:图8:综合设置页面。假设并行侧的时钟频率是60MHz,这样串行LVDS的速率是480Mbps。为方便描述,这里只针对1路LVDS数据进行设计。首先根据LVDS95的时序进行Stratix III中的LVDS模块(ALTLVDS)的调用。图9:频率和锁相环设置页面。在图8的综合设置页面中,我们没有选上“Implement Serializer/Deserializer circuitry in logic cells",这样就用到了LVDS SERDES硬核。同样也没有选上“Enable Dynamic Phase Alignment mode”选项,这表示不使用DPA功能。图10:接

在FPGA中实现源同步LVDS接收正确字对齐,标签:eda技术,eda技术实用教程,http://www.88dzw.com图8:综合设置页面。

假设并行侧的时钟频率是60MHz,这样串行LVDS的速率是480Mbps。为方便描述,这里只针对1路LVDS数据进行设计。

首先根据LVDS95的时序进行Stratix III中的LVDS模块(ALTLVDS)的调用。

图9:频率和锁相环设置页面。

在图8的综合设置页面中,我们没有选上“Implement Serializer/Deserializer circuitry in logic cells",这样就用到了LVDS SERDES硬核。同样也没有选上“Enable Dynamic Phase Alignment mode”选项,这表示不使用DPA功能。

图10:接收器设置页面。

在图9中,根据LVDS95的输出时序,在“What is the phase alignment of 'rx_in' with respect to the rising edge of 'rx_inclock'? ”里选择了0度。在图10的设置中,通常情况下需要选上“Register outputs”选项。但因为后续设计逻辑包含了这些寄存器,所以这里选择该选项。此外,在这里没有使能“rx_channel_data_align”端口来进行字重新对齐。

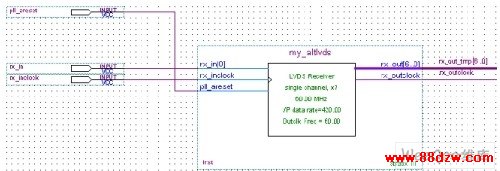

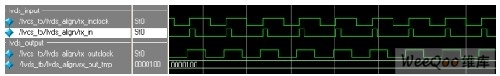

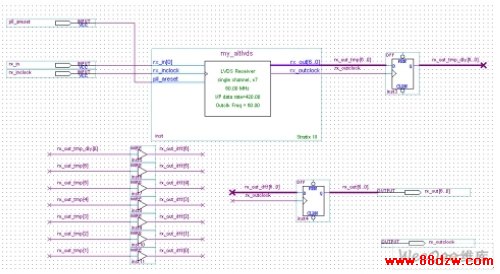

接下来需要通过仿真找出串行因子等于7的情况下,LVDS硬核的字顺序情况。图11给出了顶层设计例子,图12是在MODELSIM里的仿真结果。

图11:顶层模块的设计。

从图11的仿真波形可以看到,LVDS时钟上升沿之后的第一个数据将在并行侧的rx_out_tmp[6:0]中的rx_out_tmp[2]出现。结合LVDS95的特性,LVDS95输出的MSB(D6)将在rx_out_tmp[0]出现,于是需要将此输出滑动一位,得到正确的字顺序。

图12:仿真波形。

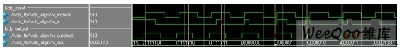

在图13中,首先将数据进行一拍延时,得到rx_out_tmp_dly[6:0],然后将rx_out_tmp_dly[0]放置在输出数据的最高位,rx_out_tmp[6:1]顺序放置在其他位上,得到数据向右滑动一位的效果。如果需要滑动多位,调整上述的放置位置就可以了。对上述调整逻辑,我们可以进一步通过仿真来验证。在此我们输入了一个计数器数据进行确认。图14给出了仿真的部分输出结果,图中,左边两根竖条标出了LVDS输入的“000001”数据,右边的两个竖条标出了rx_out的正确输出。这证明了我们的调整是正确的。

图13:字顺序的调整逻辑。

图14:内容为计数器的仿真输出波形。

本文小结

在利用Stratix III做LVDS接收时,我们可以将解串行化因子设置成等于输入的LVDS数据和时钟之间的倍数关系,这样就可以得到确定的字输出顺序,从而可以不依赖训练码实现正确LVDS接收的字对齐。此方法不仅适合于FPGA与单独的LVDS发送器进行对接,也可用于FPGA与FPGA之间的数据传送,使用时FPGA的LVDS发送端送出低频的源同步时钟即可。(Altera公司)

《在FPGA中实现源同步LVDS接收正确字对齐》相关文章

- › 在FPGA中实现PCI Express桥接解决方案

- › 在FPGA中实施4G无线球形检测器

- › 在FPGA中实现源同步LVDS接收正确字对齐

- › 雷达视频积累算法在FPGA上的实现

- › CVSD算法分析及其在FPGA中的实现

- › IIR数字滤波器设计-在FPGA上实现任意阶IIR数字滤波器

- 在百度中搜索相关文章:在FPGA中实现源同步LVDS接收正确字对齐

- 在谷歌中搜索相关文章:在FPGA中实现源同步LVDS接收正确字对齐

- 在soso中搜索相关文章:在FPGA中实现源同步LVDS接收正确字对齐

- 在搜狗中搜索相关文章:在FPGA中实现源同步LVDS接收正确字对齐

当前位置:

当前位置: