在FPGA中实现源同步LVDS接收正确字对齐

[09-12 18:28:51] 来源:http://www.88dzw.com EDA/PLD 阅读:8930次

文章摘要:在串行数据传输中,数据接收端需要一些特定的信息来恢复出正确的字边界,以确定串行码流中哪些比特属于原始并行数据里的同一时钟节拍里的数据,这一处理过程称为字对齐(Word Aligner)。一些标准的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。FPGA对上述两种方案都可以进行正确处理。那么,如何FPGA中利用低频源同步时钟实现低压差分信号(LVDS)接收字对齐呢?在串行数据传输中,数据接收端需要一些特定的信息来恢复出正确的字边界,以确定串行码流中哪些比特属于原始

在FPGA中实现源同步LVDS接收正确字对齐,标签:eda技术,eda技术实用教程,http://www.88dzw.com在串行数据传输中,数据接收端需要一些特定的信息来恢复出正确的字边界,以确定串行码流中哪些比特属于原始并行数据里的同一时钟节拍里的数据,这一处理过程称为字对齐(Word Aligner)。一些标准的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。FPGA对上述两种方案都可以进行正确处理。那么,如何FPGA中利用低频源同步时钟实现低压差分信号(LVDS)接收字对齐呢?

在串行数据传输中,数据接收端需要一些特定的信息来恢复出正确的字边界,以确定串行码流中哪些比特属于原始并行数据里的同一时钟节拍里的数据,这一处理过程称为字对齐(Word Aligner)。一些标准的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。FPGA对上述两种方案都可以进行正确处理。对于标准协议,FPGA通常都会有知识产权(IP)模块提供。本文主要讨论在FPGA中利用低频源同步时钟实现低压差分信号(LVDS)接收字对齐的设计方法及步骤。

LVDS已经成为业界高速传输最普遍应用的差分标准。LVDS的优势包括:由于采用差分信号带来的对共模噪声的免疫能力,进而提高了抗噪声能力;功率消耗较小,噪声较小等。由于LVDS有比较好的抗躁声特性,它可以采用低至几百毫伏的信号摆幅,进而可以支持更高的数据速率。

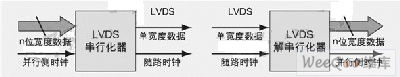

LVDS串行器/解串器(SERDES)可以完成多位宽度的并行信号到LVDS串行信号的转换以及反方向操作,如图1所示。有些器件提供图1中的随路时钟,但有些器件可能并不提供,这时LVDS解串器还必须具有时钟恢复(CDR)功能。市面上有各种规格的LVDS SERDES器件,此外FPGA或其它一些器件也都能集成LVDS SERDES模块。

图1:LVDS串行器/解串器的功能示意图。

为确保正确的数据传送,通过LVDS接收器后必须能恢复字顺序,即输入到LVDS串行器的最高比特能够正确地出现在解串器恢复输出数据的最高比特位置上,至少是需要预先知道出现在哪个比特位置上后再进行调整。图2和图3分别给出了4位宽度下字顺序得到保留和没有得到保留的例子。对于图3的情况,需要采用一种方法找把字顺序调整过来。

图2:字顺序得到保留。

图3:字顺序没有得到保留。

字顺序的调整通常采用寻找训练码来进行。一些标准的协议通常会定义特殊的码型来进行字对齐处理,比如8B/10B编码中K28.5码型的主要功能就是字对齐处理。发送端在有效数据中插入K28.5码型,接收端在收到的数据中寻K28.5码型,找到之后以这个码型为参考得到正确的并行数据输出。此外,诸如SDH协议就利用帧头位置的A1A2字节来进行字对齐处理。

另外一些相对低速的LVDS接口也利用低频的源同步时钟来携带字对齐信息,以便在接收端实现正确的数据恢复。这里的低频源同步时钟也如图1中的随路时钟,LVDS数据和随路时钟之间的倍数关系通常等于LVDS串行化时的倍数因子。比如,德州仪器(TI)的SN65LVDS95 LVDS发送器,不仅可完成21:3的LVDS串行化发送,还将21位的并行数据和时钟串行化成3路LVDS数据输出和1路时钟输出。串行化因子的值等于7,所以输出时钟的频率是LVDS数据速率的七分之一。通过这个随路时钟,配套的解串器SN65LVDS96就能够正确恢复并行数据。

《在FPGA中实现源同步LVDS接收正确字对齐》相关文章

- › 在FPGA中实现PCI Express桥接解决方案

- › 在FPGA中实施4G无线球形检测器

- › 在FPGA中实现源同步LVDS接收正确字对齐

- › 雷达视频积累算法在FPGA上的实现

- › CVSD算法分析及其在FPGA中的实现

- › IIR数字滤波器设计-在FPGA上实现任意阶IIR数字滤波器

- 在百度中搜索相关文章:在FPGA中实现源同步LVDS接收正确字对齐

- 在谷歌中搜索相关文章:在FPGA中实现源同步LVDS接收正确字对齐

- 在soso中搜索相关文章:在FPGA中实现源同步LVDS接收正确字对齐

- 在搜狗中搜索相关文章:在FPGA中实现源同步LVDS接收正确字对齐

当前位置:

当前位置: