复用器重构降低FPGA成本

[09-12 18:31:49] 来源:http://www.88dzw.com EDA/PLD 阅读:8688次

文章摘要:图4 生成复用器总线--- 2.2 复用器树--- 设计中复用器之间的馈入是常见的现象。例如,在一段HDL代码中,如下面的图3所示,if-then-else声明中含有case声明就会产生这种现象。--- 在复用器重构算法中,识别出较大的复用器树对于尽可能减少面积是非常重要的。--- 2.3 复用器总线--- VHDL信号或Verilog线宽通常会超过一个比特位。当采用if-then-else和case声明时,将会生成大量具有不同数据输入的相同复用器树,图4是一个实例。一组具有相同结构的复用器称为复用器树总线。--- 本文阐述的复用器重构技术采用了新的对整个复用器总线进行优化的方法,它通过由4.

复用器重构降低FPGA成本,标签:eda技术,eda技术实用教程,http://www.88dzw.com图4 生成复用器总线

--- 2.2 复用器树

--- 设计中复用器之间的馈入是常见的现象。例如,在一段HDL代码中,如下面的图3所示,if-then-else声明中含有case声明就会产生这种现象。

--- 在复用器重构算法中,识别出较大的复用器树对于尽可能减少面积是非常重要的。

--- 2.3 复用器总线

--- VHDL信号或Verilog线宽通常会超过一个比特位。当采用if-then-else和case声明时,将会生成大量具有不同数据输入的相同复用器树,图4是一个实例。一组具有相同结构的复用器称为复用器树总线。

--- 本文阐述的复用器重构技术采用了新的对整个复用器总线进行优化的方法,它通过由4.1节中进一步阐述的总线识别和形成技术来实现。

--- 2.4 复用器代价

--- 在许多情况下,每个2:1复用器都需要一个单独的4-LUT。这样,图1和图2中的复用器结构都需要三个4-LUT。尽管这些结构控制编码不同,但是它们都具有4个不同的数据输入,因此可以当作4:1复用器。本节阐述如何实现只需要两个4-LUT的4:1复用器。

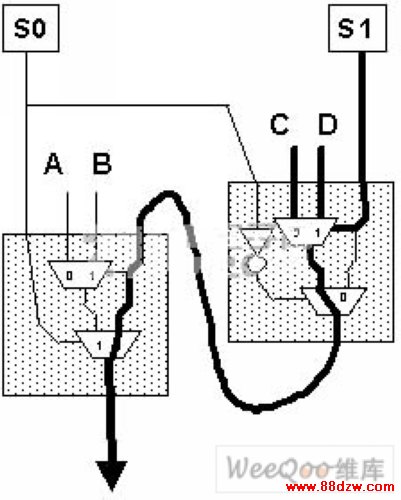

--- 图5是控制输入S0低电平时,一个有效的4:1复用器是如何工作的。4:1复用器由两个链接在一起的4-LUT(阴影框所示)构成。每个4-LUT被设置为含有阴影框中的逻辑功能。如白框所示,复用器含有四个输入――a、b、c和d,以及两个控制输入――S0和S1。

图5

--- S0低电平时,低位控制比特S1在输入c和d中进行选择,其结果通过第二个4-LUT,将a或者b输入旁路。

图6

--- 图6是控制输入S0高电平时,一个有效的4:1复用器是如何工作的。低位控制比特S1旁路c和d输入,直接进入第二个4-LUT,对a或者b输入进行选择,其结果成为第二个4-LUT的输出。

--- 第3节描述的压缩算法采用这种有效的4:1复用器,重新实现复用器结构,达到了减小面积的目的。

3. 压缩

--- 压缩是将低效的4:1复用器实现转换为高效实现的过程。复用器重构算法的面积节省由压缩实现。但是,在不同的复用器表征中进行转换,通常需要附加控制逻辑。实际上,由于附加逻辑结构抵消了使用高效复用器结构的优势,这种转换很少能够产生真正的面积节省。而复用器重构算法采用新颖的将整个复用器总线进行转换的方法,这样,总线上的多个复用器可以共享控制逻辑,因此,改善后的复用器结构优势可通过总线上的每个复用器来实现。

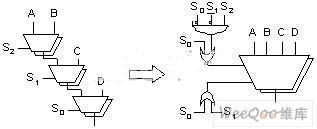

图7

--- 图7显示了如何将三个2:1复用器组成的优先级链转换为一个4:1二进制复用器。假设控制输入由不相关的逻辑馈入,那么这种转换至多需要两个额外的4-LUT控制逻辑。如果最初的复用器至少占用三个4-LUT,而4:1复用器只需要两个即可实现,那么这种转换将节省3宽度或者更宽总线的面积。

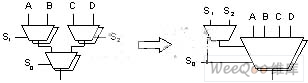

图8

--- 图8显示了如何将一组排列成树的2:1复用器转换为一个4:1复用器。在这种情况下,通过仔细为4:1复用器选择编码方式,使S0在(A、B)和(C、D)之间进行选择,限制附加控制逻辑,只加入最多一个4-LUT。此时,这种转换将节省2宽度或者更宽总线的面积。

《复用器重构降低FPGA成本》相关文章

- › 复用器重构降低FPGA成本

- 在百度中搜索相关文章:复用器重构降低FPGA成本

- 在谷歌中搜索相关文章:复用器重构降低FPGA成本

- 在soso中搜索相关文章:复用器重构降低FPGA成本

- 在搜狗中搜索相关文章:复用器重构降低FPGA成本

当前位置:

当前位置: