复用器重构降低FPGA成本

[09-12 18:31:49] 来源:http://www.88dzw.com EDA/PLD 阅读:8688次

文章摘要:图10 复用器树次优压缩的例子图11 由均衡未完善压缩图12 均衡算法图 13重构4个复用器实现均衡图14 重构5个复用器实现均衡5. 算法总结--- 本文引入了复用器树总线概念,描述了可用来提高压缩性能的均衡方法,压缩以效率更高的4:1复用器来替代2:1复用器三联。图15显示了全部复用器重构算法。--- 复用器重构算法性能依赖于对较大复用器树总线的识别。由于复用器重构算法在整个总线上分担控制逻辑,因此,总线越宽,压缩的效果就越明显。优化会减小复用器树间的相似性,从而减小所寻找的总线宽度,因此在复用器重构之前,应尽量避免优化。--- 复用器重构以分解大的复用器为2:1复用器开始。设计中所有2:

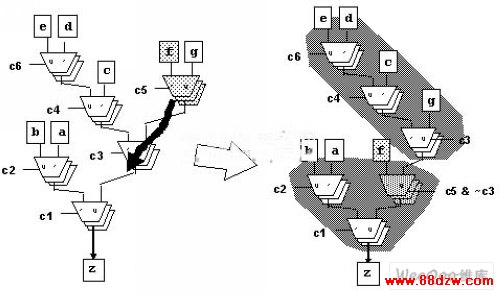

复用器重构降低FPGA成本,标签:eda技术,eda技术实用教程,http://www.88dzw.com 图10 复用器树次优压缩的例子

图11 由均衡未完善压缩

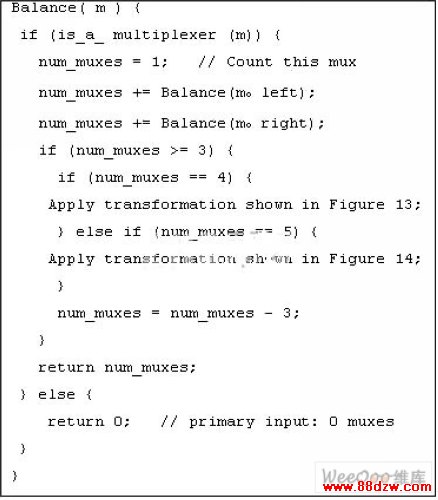

图12 均衡算法

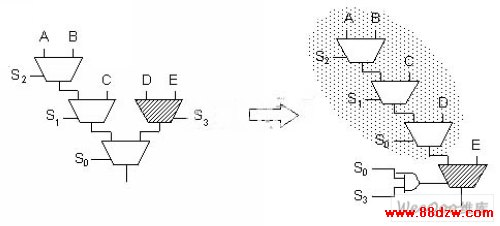

图 13重构4个复用器实现均衡

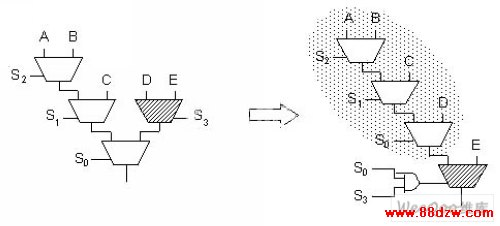

图14 重构5个复用器实现均衡

5. 算法总结

--- 本文引入了复用器树总线概念,描述了可用来提高压缩性能的均衡方法,压缩以效率更高的4:1复用器来替代2:1复用器三联。图15显示了全部复用器重构算法。

--- 复用器重构算法性能依赖于对较大复用器树总线的识别。由于复用器重构算法在整个总线上分担控制逻辑,因此,总线越宽,压缩的效果就越明显。优化会减小复用器树间的相似性,从而减小所寻找的总线宽度,因此在复用器重构之前,应尽量避免优化。

--- 复用器重构以分解大的复用器为2:1复用器开始。设计中所有2:1复用器都用于形成4.1节所描述的复用器树。结构相似的复用器树然后合并形成4.1节中的总线结构。

--- 算法的主要部分依次优化每一个总线。均衡将2:1复用器重新排列为三联,这样在压缩阶段,每个三联能够重新编码为效率更高的4:1复用器。

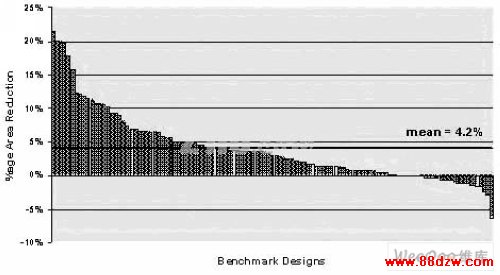

图16 复用器重构基准测试结果

6. 结果

--- 本文所阐述的算法已经集成到Altera Quartus II 4.2综合软件中。图16显示120个真实用户设计中,Altera基准测试的面积减小结果。

--- 结果表明,一小部分设计所需的LUT数量减小了20%,超过四成的设计面积减小了5%以上。所有设计面积平均减小了4.2%。

--- 据估算,面积减少平均4.2%意味着复用器平均减少了17%。

--- 复用器重构主要集中在减小面积上(例如,减少所需4-LUT的数量),而且对电路速率影响不大,电路平均速率仅降低1%。

7. 结论

--- 本文阐述了复用器重构算法,该算法能够将设计中实现复用器所需的4-LUT数量平均减少17%。

--- 复用器重构算法的关键在于优化复用器总线。即使附加了控制逻辑,新优化算法仍能够减小总线上每个比特位的面积。这是由于控制逻辑可以由总线共享,其面积代价可以抵消。

--- 压缩将2:1复用器三联转换为有效的4:1复用器。尽管可能需要附加LUT对4:1复用器控制线进行重新编码,这种代价可以通过采用复用器总线整体压缩方法来抵消。此外,通过构建最大的复用器树,可对大量的2:1复用器三联进行转换。

--- 本文还引入了能够提高压缩算法效率的均衡方法。本文描述了面向基于4-LUT的FPGA算法,例如Altera Stratix I和Cyclone器件。新的FPGA体系结构可使用不同大小的查找表(如Stratix II体系结构能够采用4、5、6输入LUT)。可采用本文阐述的方法来进一步减小这些体系结构的面积。

《复用器重构降低FPGA成本》相关文章

- › 复用器重构降低FPGA成本

- 在百度中搜索相关文章:复用器重构降低FPGA成本

- 在谷歌中搜索相关文章:复用器重构降低FPGA成本

- 在soso中搜索相关文章:复用器重构降低FPGA成本

- 在搜狗中搜索相关文章:复用器重构降低FPGA成本

当前位置:

当前位置: