基于FPGA 的多时钟片上网络设计

[09-12 18:32:58] 来源:http://www.88dzw.com EDA/PLD 阅读:8457次

文章摘要:L = 7×H + B/w (1)公式(1)中,B 是数据包的字节数,w 是每个时钟周期转换的字节数。参数7 是在多时钟片上网络路由器中安装在每个路由器跳延迟支付。这个延时是因为基于数据包中的头数据片的解码和仲裁执行所导致的。为了*估所设计的多时钟架构的性能, 将利用所设计的路由器的VHDL 模型,模拟一个3×3Mesh 结构,在本身频率下执行包装产生的数据包。路由器的频率值会在拓扑结构合成,布局和布线阶段完成之后得出。对于不同的配置(资源的可用性、跨路由器的距离、bRA

基于FPGA 的多时钟片上网络设计,标签:eda技术,eda技术实用教程,http://www.88dzw.comL = 7×H + B/w (1)

公式(1)中,B 是数据包的字节数,w 是每个时钟周期转换的字节数。参数7 是在多时钟片上网络路由器中安装在每个路由器跳延迟支付。这个延时是因为基于数据包中的头数据片的解码和仲裁执行所导致的。

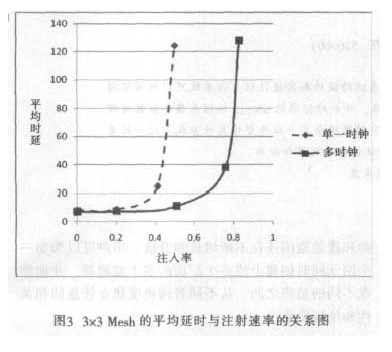

为了*估所设计的多时钟架构的性能, 将利用所设计的路由器的VHDL 模型,模拟一个3×3Mesh 结构,在本身频率下执行包装产生的数据包。路由器的频率值会在拓扑结构合成,布局和布线阶段完成之后得出。对于不同的配置(资源的可用性、跨路由器的距离、bRAM/dRAM FIFO 的版本),路由器的频率可以降低高达18%[6]。图3 显示了单一时钟与多时钟,在延时与注射速率关系中的曲线图。在单一时钟时,网络的频率为286MHz。而在多时钟时, 频率的范围是从286MHz~357MHz。图3 中,X 轴表示的注射率是在一个周期内每个节点注入flit 的数量。Y 轴曲线测量的是每个实例中数据包的平均延时。可以看出,所提出的多时钟片上网络相比单一时钟片上网络的性能显着增加。

4 结语

本文介绍了一个基于FPGA 的高效率多时钟的虚拟直通路由器,通过优化中央仲裁器和交叉点矩阵,以争取较小面积和更高的性能。同时,扩展路由器运作在独立频率的多时钟NoC 架构中,并在一个3×3Mesh 的架构下实验,分析其性能特点,比较得出多时钟片上网络具有更高的性能。

Tag:EDA/PLD,eda技术,eda技术实用教程,EDA/PLD

《基于FPGA 的多时钟片上网络设计》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA 的多时钟片上网络设计

- 在谷歌中搜索相关文章:基于FPGA 的多时钟片上网络设计

- 在soso中搜索相关文章:基于FPGA 的多时钟片上网络设计

- 在搜狗中搜索相关文章:基于FPGA 的多时钟片上网络设计

分类导航

最新更新

当前位置:

当前位置: