Verilog HDL语言在FPGA/CPLD开发中的应用

[11-20 16:12:57] 来源:http://www.88dzw.com FPGA 阅读:8392次

文章摘要:always@(posedge clk or negedge rst) if(!rst) begin state<=IDLE; end else casex(state) IDLE:if(x==0) state<=A; else state<=IDLE; A:if(x==1) state<=B; else state<=A; B:if(x==1) state<=C; else state<=F; C:if(x==0) state<=D; else state<=G; D:if(x==1) state<=E; else state<

Verilog HDL语言在FPGA/CPLD开发中的应用,标签:fpga是什么,fpga教程,http://www.88dzw.comalways@(posedge clk or negedge rst)

if(!rst)

begin

state<=IDLE;

end

else

casex(state)

IDLE:if(x==0)

state<=A;

else state<=IDLE;

A:if(x==1)

state<=B;

else state<=A;

B:if(x==1)

state<=C;

else state<=F;

C:if(x==0)

state<=D;

else state<=G;

D:if(x==1)

state<=E;

else state<=A;

E:if(x==1)

state<=C;

else state<=A;

F:if(x==0)

state<=A;

else state<=B;

G:if(x==0)

state<=F;

else state<=G;

default: state<=IDLE;

endcase

endmodule

由上述这个程序可以看出:Verilog HDL程序是由模块构成的。每个模块的内容都是嵌在module和endmodule两个语句之间实现特定的功能的。每个模块都由两部分组成,一部分描述接口;另一部分描述逻辑功能,即定义输入是如何影响输出的。如程序中的sequdet(x,z,clk,rst)就是模块的端口,声明了模块的输入、输出口。接下来就是模块中最重要的部分逻辑功能的定义。在模块中产生逻辑,Verilog HDL语言有3种方法:

(1)用“assign”声明语句。这种方法很简单,只需写一个“assign”,后面再加一个方程式即可。这也是最常用的方法之一。如程序中的assign z==(state==D && x==1)?1:0;就表示状态为D时又收到了1,表明收到“01101”应使Z输出为高电平。

(2)用“always”块。它常被用来描述时序逻辑,上面的程序中即用这个模块完成了状态机的状态转化功能。

(3)采用实例元件的方法。这时只要键入元件的名字和相连的引脚即可。这样就可以用上面这不长的程序,完成这个对序列的检测功能,并且逻辑描述也十分容易理解。

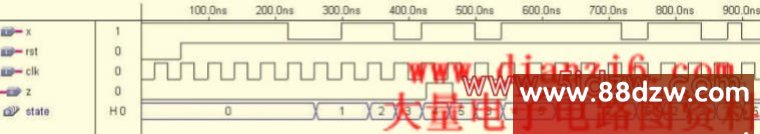

上述程序输入完成后,接下来首先要经EDA设计软件进行编译。本设计采用的是美国ALTERA公司的MAX+PLUSII软件,经Compiler编译器编译,没有任何问题后。建网表、逻辑综合、适配、划分、时域分析、装配等均已自动完成,并生成多个后续工作要用的文件。编译成功表明已为所设计的项目建立了一个编程文件,但还不能说明该文件在各种情况下都有正确的响应,因此编译通过后还要进行功能和时序仿真,仿真结果如图2所示。

经仿真发现输出Z和输入X有一段延时。通过波形很难给出定量的信号延时关系,为此我们在进行定时分析。定时分析结果如图3所示,从表中显示出了“CLK”到“Z”的延迟路径为7.6ns、“X”到“Z”的延迟路径为6ns。这样,经Verilog HDL语言的文本编辑、编译、仿真波形编辑、仿真和定时分析一系列设计步骤,设计出符合要求的数字系统后就可以通过编程器下载到指定的芯片中去。

综上所述,则更能体会到Verilog HDL语言的优势:由于它在其门级描述的底层,也就是晶体管开关的描述方面比VHDL等各种其它的HDL语言有更强的功能。所以在复杂数字逻辑电路和系统的设计仿真时更有优势;描述的设计思想、电路结构和逻辑关系清晰明了,并且设计语言简练、易学易用;其模块化分层结构在大规模设计时更能体现出优势。因此可以看出,Verilog HDL语言在EDA设计中相对与其他的各种硬件描述语言更有优势。

3 结束语

随着集成电路规模的越来越大,数字系统设计的越来越复杂,Verilog HDL语言在硬件电路设计的优越性也会越来越显突出。目前,数百万门规模的FPGA/CPLD已进入实用,Verilog HDL强大的系统描述能力、规范的设计结构和简洁、灵活的编程风格会使其必将能会用来完成大数字系统、超大规模数字系统的几乎全部设计任务。

参考文献

1 夏宇闻.复杂数字电路与系统的Verilog HDL 设计.北京航空航天大学出版社,1998

2 王诚,薛小刚,钟信潮.FPGA/CPLD设计具XILINX ISE5.X使用详解.北京人民邮电出版

社,2003

3 侯伯亨,顾新.VHDL硬件描述语言与数字逻 辑电路设计.西安电子科技大学出版社,1997

4 夏宇闻.Verilog数字系统设计教程.北京航 天航空大学出版社,2003

《Verilog HDL语言在FPGA/CPLD开发中的应用》相关文章

- › 基于Verilog HDL的UART模块设计与仿真

- › verilog PS2键盘解码程序

- › 好用的Verilog串口UART程序

- › 怎样实现Verilog模拟PS2协议

- › 基于VerilogHDL的背景噪声扣除电路设计

- › 对C语言编程者的Verilog开发指南实例

- 在百度中搜索相关文章:Verilog HDL语言在FPGA/CPLD开发中的应用

- 在谷歌中搜索相关文章:Verilog HDL语言在FPGA/CPLD开发中的应用

- 在soso中搜索相关文章:Verilog HDL语言在FPGA/CPLD开发中的应用

- 在搜狗中搜索相关文章:Verilog HDL语言在FPGA/CPLD开发中的应用

当前位置:

当前位置: