��XC9572ʵ��HDB3��������

[11-20 16:15:06] ��Դ��http://www.88dzw.com FPGA �Ķ���8292��

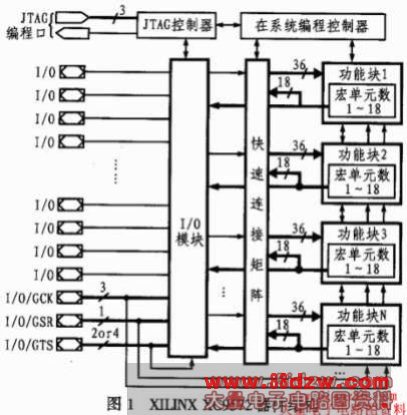

����ժҪ��ժҪ��������HDB3������ԭ���ͷ�������������CPLD��Complex Programmable Logic Device��ʵ��E1�ź�HDB3�����ķ�����ͬʱ����������ʵ��ԭ��ͼ����������XILINX��XC9500ϵ�пɱ���������Ŀ������̡��ؼ��ʣ����ӿɱ������·�������ܶ��룻���Խ��淴ת�룻��ϵͳ��̣��أã������� �������ܣأã��������ǣأɣ̣ɣΣع�˾������һ������ܿɱ�������������ں����������֣������ܿ飬�����У�������������ϵͳ�š���ϵͳ�ṹ��ͼ����ʾ���ӽṹ�Ͽ����أã��������������ֵ�Ԫ�����굥Ԫ���ɱ�̣ɣ��ϵ�Ԫ�Ϳɱ���ڲ����ߡ�����Ҫ�ص����£������пɱ�̹ܽż�

��XC9572ʵ��HDB3��������,��ǩ��fpga��ʲô,fpga�̳�,http://www.88dzw.comժҪ��������HDB3������ԭ���ͷ�������������CPLD��Complex Programmable Logic Device��ʵ��E1�ź�HDB3�����ķ�����ͬʱ����������ʵ��ԭ��ͼ����������XILINX��XC9500ϵ�пɱ���������Ŀ������̡�

�ؼ��ʣ����ӿɱ������·�������ܶ��룻���Խ��淴ת�룻��ϵͳ���

�����أã������� ��������

�أã��������ǣأɣ̣ɣΣع�˾������һ������ܿɱ�������������ں����������֣������ܿ飬�����У�������������ϵͳ�š���ϵͳ�ṹ��ͼ����ʾ���ӽṹ�Ͽ����أã��������������ֵ�Ԫ�����굥Ԫ���ɱ�̣ɣ��ϵ�Ԫ�Ϳɱ���ڲ����ߡ�����Ҫ�ص����£�

�����пɱ�̹ܽż�ĽŶԽ���ʱ��Ϊ�����

��ϵͳ��ʱ���ٶȿɴﵽ�������ͣȣ���

����У������굥Ԫ�ͣ�������������ϵͳ�ţ�

��ɱ�̴���Ϊ�����������Σ�

��ɲ��ã������߱�̺Ͳ�����

��ӵ��ǿ��Ĺܽ�����������

��ÿ���굥Ԫ�����пɱ�̵���ģʽ��

��δ�õĹܽ��б�̽ӵ�������

���ṩ�б�̱���λ���ɶ�����ṩ���ܱ����Է�ֹ�Ƿ���ȡ��

���ⲿ�ɣ��������룳�����ֺͣ��ּ��ݡ�

�����ȣģ£��ı���뼰ʵ��ԭ��

�ȣģ£��루�����ܶ�˫�����룩�ǻ��������豸֮����л����������Ҫ����֮һ��������Ҫ�ص���������ȡʱ�ӡ�����ֱ������Ӱ�졢�����Լ����������С�ڣ����ȡ�

�ţ��ź����ҹ���ŷ���ҵ��Ŵ�����һ��Ⱥʹ�õĴ���ϵͳ���ţ��ź��ɣ��������������ģУãͻ�·����ʱ�ָ����γɡ��ããɣԣԽ���ǣ�����������ϸ�涨�ˣȣģ£������ڣţ��źŵı���

�ãأã�������ʵ�֣ţ��źŵģȣģ£�������·�Ƚϼ���������ɵ�����Χ��·�������ʹ���ˣУã�����װ��ʽ�ģأã��������ɱ�����������У������ɱ�̣ɣ����š�������Դ���źͣ����ʣԣ������š��������ʹ���ˣأã�������������������������ͼ����ʾ����ʵ����·ͼ��

�ȣģ£����ǣ��ͣɣ�������������� �ͣ��� �ɣ����������ĸĽ��͡����ͣ������ý��漫�Ե������ʾ��Ԫ�����������������ʾ��Ԫ��������Ϊ�˷�ֹ��·��ʱ�����������״̬���ȣģ£���ı�������ǣ���û�У����������ġ�������ʱ���Ͱ����ͣ��������룻�����֣����������ġ�������ʱ��ÿ���������������ĵ�һ���������ı仯Ӧ����ǰ�����ڵġ�����������������������ǰһ���������ļ�����ǰһ���ƻ���ļ����෴�����������ƻ��㣬�������ġ������ĵ�һ���Ա��֡��������������ǰһ���������ļ�����ǰһ���ƻ���ļ�����ͬ�����������ƻ��㣬���һ����������Ϊ����������һ����֤������ƻ�����н���ļ��ԣ������������ֱ���ɷ֡����������������ĵڣ����������ǡ����������������ġ������ĵڣ�����Ϊ������������������ǰһ���������ļ�����ͬ���ƻ��㼫�Խ�������ڽ��նˣ������̽��յ�����������ͬ�ġ�����������ǰ���У��������ġ���������һ����������Ϊ���������������ǰ���У��������ġ���������ǰ��������������Ϊ�������������ͻָ���ԭ���������źš�������һ���ȣģ£�������ӣ�

����XC9572ʵ��HDB3�������ơ��������

- › ��XC9572ʵ��HDB3��������

- �ڰٶ�������������£���XC9572ʵ��HDB3��������

- �ڹȸ�������������£���XC9572ʵ��HDB3��������

- ��soso������������£���XC9572ʵ��HDB3��������

- ���ѹ�������������£���XC9572ʵ��HDB3��������

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

��ǰλ�ã�

��ǰλ�ã�