����ģ�����Ƶij�����ͬ��������FPGAʵ��

[11-20 16:15:04] ��Դ��http://www.88dzw.com FPGA �Ķ���8207��

����ժҪ��ժҪ�������˳�����ͬ�����Ļ�������ԭ����������ڳ�����ͬ����������ģ�������ƻ�ý�С��λ�����ķ����������˳�����ͬ�����ڣƣУǣ��ϵľ���ʵ�֡��ؼ��ʣ�����ͬ�� ģ������ �ƣУǣ�������ͨ��ϵͳ�У������Է������ʶԽ������������������Եز�����Ϊ�ˣ���������Ҫһ������ʱ���źţ����ʱ���źŵ�Ƶ�ʺͷ���������ȣ���λ����뱣֤����ʱ������ѵġ��ڽ������л���������ʱ�ӵĹ��̱���Ϊ����ͬ������Ŷ�ʱ�ָ��������ţ��ţ������������ �ǣ���壩��ʵ�ַ���ͬ������Ҫ����֮һ���㷺�����ڸ�������ͨ��ϵͳ�С���������Ļ���ģ�����Ƶij������봫ͳ�ij�������ȣ�����ͬ���ٶȿ졢����С����λ����С���ŵ㡣��

����ģ�����Ƶij�����ͬ��������FPGAʵ��,��ǩ��fpga��ʲô,fpga�̳�,http://www.88dzw.comժҪ�������˳�����ͬ�����Ļ�������ԭ����������ڳ�����ͬ����������ģ�������ƻ�ý�С��λ�����ķ����������˳�����ͬ�����ڣƣУǣ��ϵľ���ʵ�֡�

�ؼ��ʣ�����ͬ�� ģ������ �ƣУǣ�

������ͨ��ϵͳ�У������Է������ʶԽ������������������Եز�����Ϊ�ˣ���������Ҫһ������ʱ���źţ����ʱ���źŵ�Ƶ�ʺͷ���������ȣ���λ����뱣֤����ʱ������ѵġ��ڽ������л���������ʱ�ӵĹ��̱���Ϊ����ͬ������Ŷ�ʱ�ָ��������ţ��ţ������������ �ǣ���壩��ʵ�ַ���ͬ������Ҫ����֮һ���㷺�����ڸ�������ͨ��ϵͳ�С���������Ļ���ģ�����Ƶij������봫ͳ�ij�������ȣ�����ͬ���ٶȿ졢����С����λ����С���ŵ㡣����ƣУǣ�ʵ���У�������������ʵʱ������Ƶķ����������ʵ��Ӧ�õ�����������Ʊ�ת��Ϊ�����̣���һ�����˵�·��

�� �����ż��

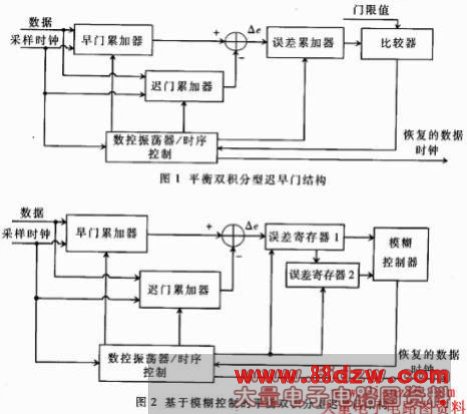

һ�ױջ�ƽ��˫�����ͳ����Žṹ��ͼ����ʾ��

�����ۼ����ͳ����ۼ����ֱ������������İ���������ڶ��������ݵIJ���ֵ�����ۼӣ�������ǰ��������ںͺ����������ڽ��յ����źŵ�������������һ����������ͬ��������λ�������Ϊ�˱�֤��λ������Ч�ԣ�����ʱ�ӵ�Ƶ�ʱ����Ƿ������ʵ�ż������һ������ҪΪ������������յ����ź�Ϊ�����ģ�����ô��λ����Ϊ�㣻������յ����ź��У�����������֣���ô��λ������ܲ�Ϊ�㡣����ۼ����ͱȽ���������һ��ͨ��·�˲�������λ����ۼ�ֵ��һ������ֵ�Ƚϣ������IJ�ֵ���Ʊ������ɵ�����ʱ����λ����λ����ۼ�ֵ�ķ��ž�������ʱ�ӵ���λ��ǰ�ƻ��Ǻ��ƣ�ÿ����λ�����ķ����ǹ̶��ģ�����������ֵҲ�ǹ̶��ġ����������ݱ������ɵ�����ʱ�Ӿ��������ۼ����������ۼ���������ۼ����Ĺ���ʱ��

�������ŵIJ�������Ϊ�ԣ����������ĵ�������Ϊ�䣬�����ڳ�������λ������ɵĽ�������ʱ�ӵ���λ����Ϊ�䡤�ԣ�����������ȣ�ϴ�������ʱ�ӿ��Ժܿ��ͬ���ϣ�������λ�����ͻ�Ƚϴ�����������ȣ��С������λ������С����������ʱ�ӿ�����Ҫ�ϳ���ʱ����ͬ����

�� �����ŵ�ģ���������

ͬ���ٶȺ���λ��������Լ���������ܵ�����ߵ���Ҫ���ء�Ϊ��ʵ�ֽ�С��λ����Ҫ���µĿ���ͬ�������Բ�������Ӧ����������λ����ʹ�ýϴ�ĵ������ȣ�����λ���ٽ�ʹ�ý�С�ĵ������ȡ����������һ�ֻ���ģ�����Ƶķ�����ͬ�����Դﵽ����Ӧ��Ч��������³���Ժá�����ʵ�֡�

����ģ�����Ƶ�ƽ��˫�����ͳ����Žṹ��ͼ����ʾ��

�ڽṹ�ϣ�����ģ�����Ƶij�������������λ���Ĵ���ȡ���˴�ͳ�����ŵ���λ����ۼ�������һ�������롢�������ģ��������ȡ���˴�ͳ�����ŵļȽ�������ģ��������������Ϊ��λ����ۼ�ֵ�ĵ�ǰֵ���壨���ǰһ�μ���ֵ���壨����������Ϊ���������ĵ�������ֵ�䡣�������������Ⱥ����������������ģ���ָ�Ϊ���Σ£�����С���Σӣ����㣨�ڣң�����С���Уӣ������У£�����ȡֵ��ģ���ָ��ͼ�α�ʾ��ͼ����ʾ����������䱻ģ���ָ�Ϊ���Σ£������У��Σͣ�����С���Σӣ����㣨�ڣң�����С���Уӣ������У��Уͣ������У£�����ȡֵ��ģ���ָ��ͼ�α�ʾ��ͼ����ʾ��

ģ���������Ŀ��ƹ�����������ʾ��

- ��һƪ��HDLC��FPGAʵ�ַ���

������ģ�����Ƶij�����ͬ��������FPGAʵ�֡��������

- › ����ģ�����Ƶij�����ͬ��������FPGAʵ��

- �ڰٶ�������������£�����ģ�����Ƶij�����ͬ��������FPGAʵ��

- �ڹȸ�������������£�����ģ�����Ƶij�����ͬ��������FPGAʵ��

- ��soso������������£�����ģ�����Ƶij�����ͬ��������FPGAʵ��

- ���ѹ�������������£�����ģ�����Ƶij�����ͬ��������FPGAʵ��

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

��ǰλ�ã�

��ǰλ�ã�