����ģ�����Ƶij�����ͬ��������FPGAʵ��

[11-20 16:15:04] ��Դ��http://www.88dzw.com FPGA �Ķ���8207��

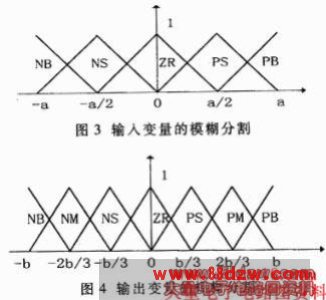

����ժҪ����1 ģ�����ƹ������λ��e(n-1)��λ��e(n)DCO��������dNBNSZRPSPBNBPBPBPMPMPSNSPBPMPMPSPSZRPMPSZRNSNMPSNSNSNMNMNBPBNSNMNMNBNB����ģ���������������ģ���ָ����������ȡֵ���У������Ľ��������Գ�����㣨�������ᣯ�������ᣩ����ľ�ȷ����ֵ����Ӧ�������ƹ���ģ������������������������������ķ����� ģ�����Ƴ����ŵģƣУǣ�ʵ����ʵ�������У���Ҫ�Խ��յ��ģ��ͣ����˹��СƵ�Ƽ��أ��ǣ����ͣӣˣ��źŽ��з���ͬ�������Ҫ��ģ�����Ƶ�Ԫ�������ٶ�����Ϊ���� �ƣ̣ɣУӣ��ƣ������� �̣������ �ɣ��

����ģ�����Ƶij�����ͬ��������FPGAʵ��,��ǩ��fpga��ʲô,fpga�̳�,http://www.88dzw.com��1 ģ�����ƹ������λ��e(n-1)

| ���e(n) | DCO��������d | NB | NS | ZR | PS | PB |

| NB | PB | PB | PM | PM | PS | |

| NS | PB | PM | PM | PS | PS | |

| ZR | PM | PS | ZR | NS | NM | |

| PS | NS | NS | NM | NM | NB | |

| PB | NS | NM | NM | NB | NB |

����ģ���������������ģ���ָ����������ȡֵ���У������Ľ��������Գ�����㣨�������ᣯ�������ᣩ����ľ�ȷ����ֵ����Ӧ�������ƹ���ģ������������������������������ķ���

�� ģ�����Ƴ����ŵģƣУǣ�ʵ��

��ʵ�������У���Ҫ�Խ��յ��ģ��ͣ����˹��СƵ�Ƽ��أ��ǣ����ͣӣˣ��źŽ��з���ͬ�������Ҫ��ģ�����Ƶ�Ԫ�������ٶ�����Ϊ���� �ƣ̣ɣУӣ��ƣ������� �̣������ �ɣ��������� ���� �ӣ����䣠����Ȼ���������������ٶ�ָ�꣬��������һ���ͨ�ô��������Ǻ���ʵ�ֵġ���ˣ�ģ�����Ƴ����ű���ʹ��Ӳ����ʵ�֡��ƣУǣ���һ�����۵İ붨�ƴ��ģ���ɵ�·�����Ŀ������߿����ڣУû������С��ƣУǣ������ܶȸߡ��ṹ�����ʱ��̺Ϳɱ�̵��ŵ㣬�dz��ʺ�����ģ�������ŵ�Ӳ����֤��

һ�����͵�ģ��������ͨ���ɰ������ƹ����֪ʶ�⡢ģ��������Ԫ�Լ����ⲿ�ӿڵ�ģ������Ԫ����������Ԫ��ɡ��ԣ�������������������ģ����������Ӳ��ʵ�ַ����Ѿ����˺ܶ���������ֵ�·ʵ��ģ���������Ѿ��зdz��������Ʒ�������Щ������ģ�����������ĸ�������Ԫ�����ֵ�·һһʵ�֣�ģ�������ٶ�Ҳ���Դﵽ���� �ƣ̣ɣУ����ϡ�������ģ�����Ƴ������У�ģ��������ֻ�����е�һ���֣�������Ҳֻ���������ջ��е�һ����Ԫ���������ͨ�õ���Ʒ��������ʵ�ֵ�ģ�����Ƴ�����ռ�ãƣУǣ�������Ԫ��Ȼ�ܶ࣬��ʹ�������ջ�ռ�õ�оƬ����ܴ���ģ���������ڳ������еĹ��ܱȽϵ�һ����ʵ�ָ��á���ˣ�ģ�����Ƴ������е�ģ����������������ͨ������Ʒ�����Ϊ�˼�Сռ�õ�оƬ�����ģ�����������������µ����˼·�����ȣ�ȷ�����������ȷ���ı�������Ȼ��������ģ�����Ʊ��������һ�����������ȷ��֮�����ֵ�������������ֵ������Ϊ�����̡�������ģ���������Ϳ����ü��������ʵ�֡���������̺�����Ӳ���������Ա�д����Ȼ���ڣƣУǣ�����ϵͳ�жԱ�õij���������������������ֵij�����б��롣�������ɹ����ƣУǣ�����ϵͳ������һ���ƣУǣ�оƬ�������ļ�������������ļ�ͨ�����õ������ص�оƬ��������յõ�һ��ʵ��ģ�����Ƴ����ŵ�оƬ��

- ��һƪ��HDLC��FPGAʵ�ַ���

������ģ�����Ƶij�����ͬ��������FPGAʵ�֡��������

- › ����ģ�����Ƶij�����ͬ��������FPGAʵ��

- �ڰٶ�������������£�����ģ�����Ƶij�����ͬ��������FPGAʵ��

- �ڹȸ�������������£�����ģ�����Ƶij�����ͬ��������FPGAʵ��

- ��soso������������£�����ģ�����Ƶij�����ͬ��������FPGAʵ��

- ���ѹ�������������£�����ģ�����Ƶij�����ͬ��������FPGAʵ��

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

��ǰλ�ã�

��ǰλ�ã�