基于SRAM的可重配置电路

[11-20 16:13:26] 来源:http://www.88dzw.com FPGA 阅读:8299次

文章摘要:基于SRAM的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路中PLD的逻辑功能创造了条件。PLD使用SRAM单元来保存字的配置数据决定了PLD内部互连和功能,改变这些数据,也就改变了器件的逻辑功能。由于SRAM的数据是易失的,因此这些数据必须保存在PLD器件以外的EPROM,EEPROM或FLASH ROM等非易失存储器内,以便系统在适当的时候将其下载到PLD中,从而实现在电路可重配置ICR(In-Circuit Reconfigurability,在电路可重配置)。如何实现ICR?ALTER公司的应用方案AN88中详细介绍一种基于DS87C520微控制器的ISP&ICR

基于SRAM的可重配置电路,标签:fpga是什么,fpga教程,http://www.88dzw.com基于SRAM的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路中PLD的逻辑功能创造了条件。PLD使用SRAM单元来保存字的配置数据决定了PLD内部互连和功能,改变这些数据,也就改变了器件的逻辑功能。由于SRAM的数据是易失的,因此这些数据必须保存在PLD器件以外的EPROM,EEPROM或FLASH ROM等非易失存储器内,以便系统在适当的时候将其下载到PLD中,从而实现在电路可重配置ICR(In-Circuit Reconfigurability,在电路可重配置)。

如何实现ICR?ALTER公司的应用方案AN88中详细介绍一种基于DS87C520微控制器的ISP&ICR设计方法,并钭其源代码放在ALTERA的网上,供用户免费下载。作者在设计一要求具有ICR功能的电子装置时,在详细分析了AN88介绍的方法之后,发现该应用方案中介绍的电路结构复杂,对微控制器性能及微控制器的开发装置的要求和成本都较高,且只适用于工作电压为5V的PLD电路。本文介绍的是作者设计的PLD ICR控制电路,它和ALTERA介绍的方法相比,不但线路结构简洁、开发容易、体积小、成本低,而且只需改变ICR控制电路的电源电压,就能实现工作电压为3.3V或5V的PLD器件的电路内重配置。

ICR控制电路硬件原理

ICR控制电路原理图如图1所示。图中的U1是ICR控制电路的核心器件,它是PHILIPS公司在1999年底推出的20引脚低成本的微控制器P87LPC762,该微控制器具有2K字节的程序存储器、128字节的RAM、18/15个I/O、WATCHDOG、通用串行接口UART和一个硬件I2C总线控制器。P87LPC762采用的是80C51加速处理器结构,其指令和80C51兼容,但指令的执行速度在相同时钟下,是标准80C51微控制器的两倍。因它采用的是硬件I2C总线控制器节省大量的软硬件资源。U2、U3是ATMEL公司的串行EEPROM AT24C256,其串行通信协议为I2C,容量为32K字节。在电路中,U2和U3有来存储PLD的配置数据。

ICR控制电路的工作过程为:经MAXPLUS Ⅱ编译生产的PLD配置文件经过预处理后,通过PC机的串行通讯口下载到U1中,并在U1的控制下存储在EEPROM U2和U3中,U1再根据系统的要求通过P0.2、P0.3、P0.4、P0.6和P0.7等5个I/O口,将其存储在U2和U3中的PLD配置数据下载到电路中的PLD。

因作者设计电路中的PLD是ALTERA公司的ACEX系列的EP1K30,其配置文件的容量为52K字节,故电路中采用了两片AT24C256存储PLD的配置数据。如果配置的PLD是EPF10K10或EPF10K20,则只需要一片AT24C256,此时整个ICR控制电路仅仅只有两片IC,这可以说它是目前结构最简单、成本最低的ICR控制电路了。读者在应用该电路时,可根据其PLD文件的大小(PLD的配置文件的大小可参考ALTERR公司的应用方案AN116)采用1~4片AT24C256。

ICR控制电路软件设计要点

在图1介绍的ICR控制电路中,其存储PLD配置数据的EEPROM AT24C256采用I2C串行总线进行数据交换,其数据交换速度较慢(当工作电压为5V时,其最大I2C总线时钟为1MHz),而PLD配置数据又比较大,通常都在数十K字节以上。因此如何提高图1介绍的ICR控制电路的配置速度,这将是软件设计上的一个重点。

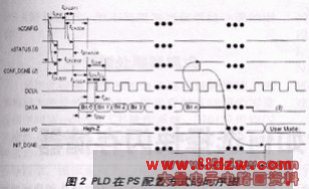

ALTERA公司生产且具有ICR功能的PLD器件有FLEX6000、FLEX10K、APEX和ACEX系列,它们的配置方式可分为PS(无源串行)、PPS(无源并行同步)、PSA(无源并行异步)、PSA(无源串行异步)和JTAG(Joint Test Action)等四种方式,在这四种方式,PS方式因PLD与配置电路的互连最简单,对配置时钟的最小频率没有限制而应用最广泛,因此在图1介绍的ICR控制电路中也采用PS配置方式来实现ICR功能。图2是PS配置方式的时序图。

《基于SRAM的可重配置电路》相关文章

- › 基于SRAM的可重配置电路

- › 基于SRAM的微控制器提供更优的安全性

- 在百度中搜索相关文章:基于SRAM的可重配置电路

- 在谷歌中搜索相关文章:基于SRAM的可重配置电路

- 在soso中搜索相关文章:基于SRAM的可重配置电路

- 在搜狗中搜索相关文章:基于SRAM的可重配置电路

当前位置:

当前位置: