����VHDL��I2C���߿��ƺ����

[11-20 16:14:10] ��Դ��http://www.88dzw.com FPGA �Ķ���8320��

����ժҪ�������I2C���ƺ�ʱ������ע�����¼������棺 ��I2C���ƺ���������Host����C6711 DSP���Լ���Ƶ���������Ӳ���ӿ����ӹ�ϵ�����ǵ�I2C����ͨ��Э���ʱ���ϵ��оƬ��/д�������̣�I2C���ƺ�Ӧ�ð���������Χ�ӿڣ���ͼ1��ʾ��һ����C6711 EMIF��External Memory Interface����չ�洢���ӿڣ��ĸ����첽�洢��ASRAM��Asynchronous SRAM���ӿڣ���Ϊ�����ӿڡ�����I2C���ƺ˷����������������ݣ��0λ��ַ���ߡ�32λ˫����̬�������ߡ��첽���ʹ���ź�aoe���첽дʹ��awe���첽��ʹ��are���ⲿ�洢���ռ�ѡͨce2���ⲿ�ж�����eint

����VHDL��I2C���߿��ƺ����,��ǩ��fpga��ʲô,fpga�̳�,http://www.88dzw.com�����I2C���ƺ�ʱ������ע�����¼������棺

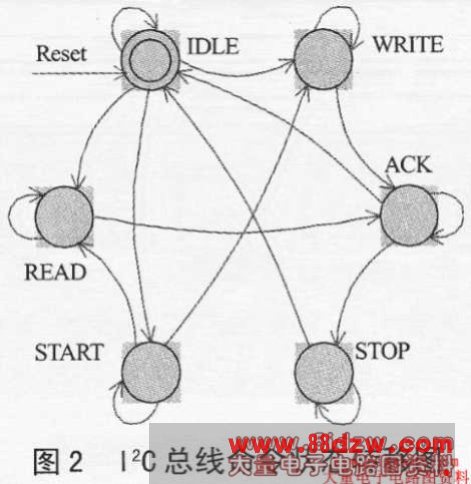

��I2C���ƺ���������Host����C6711 DSP���Լ���Ƶ���������Ӳ���ӿ����ӹ�ϵ�����ǵ�I2C����ͨ��Э���ʱ���ϵ��оƬ��/д�������̣�I2C���ƺ�Ӧ�ð���������Χ�ӿڣ���ͼ1��ʾ��һ����C6711 EMIF��External Memory Interface����չ�洢���ӿڣ��ĸ����첽�洢��ASRAM��Asynchronous SRAM���ӿڣ���Ϊ�����ӿڡ�����I2C���ƺ˷����������������ݣ��0λ��ַ���ߡ�32λ˫����̬�������ߡ��첽���ʹ���ź�aoe���첽дʹ��awe���첽��ʹ��are���ⲿ�洢���ռ�ѡͨce2���ⲿ�ж�����eint����������Ƶ��/������������I2C���߽ӿ�SCL��SDA��I2C���ƺ˳�ΪI2C���ߵ����豸��master����ʵ��EMIF��ASRAM�ӿ���I2C���߽ӿڵ�ת����I2C��������Ƶ����������Ƶ������������ΪI2CU���ߵĴ��豸��slave����

�����ͨ��������̣������ʵ�ֶԿ��ƺ��и�������IJ�����Ϊ�ˣ��ڿ��ƺ��ڲ����豸��6��8λ�Ĵ��������ڹ����������ƺ˵Ĺ�������Щ�Ĵ��������ơ���š�λ������ַ��������ʽ���Լ��Ĵ����ڲ��豸�Ŀ���λ�����ܵľ���������1���С��Ĵ����ڲ����õĿ���λ�����ܵľ���������1���С��Ĵ�����Ѱַʹ��EMIF�ӿڵ�ַ���ߵĵ���λeadd[4��2]���ɸ�λ��ַ����õ���I2C���ƺ�ʹ���ź�nce����DSP�����Ķ���д������ɺ�I2C_top����DSP���ж�����eint����DSP������һ�����CR����RXR�ж�����������������ݵ�TXR��

��1 I2Ctopģ���ڲ��Ĵ���

| �Ĵ��� | λ �� | �� ַ | �� �� |

��������� |

| ���ƼĴ���CTR | 8 | 000 | ֻд | I2C���ƺ�ʹ��λ��core-en�������ж�ʹ��λien�� |

| ����Ĵ���CR | 8 | 001 | ֻд | ������start-r��������rd-r����д��wr-r����ֹͣ��stop-r�������豸ȷ�ϣ�ack-r�����ж���Ӧλ��i-ack-r�� |

| ״̬�Ĵ���SR | 8 | 010 | ֻ�� | ���豸ȷ��λ��rx-ack����I2C-coreģ��æλ��Core-busy�� |

| ���ͼĴ���TXR | 8 | 011 | ֻд | �Ĵ������͵����豸������ |

| ���ռĴ���RXR | 8 | 100 | ֻ�� | �Ĵ��ɴ��豸��ȡ������ |

| ʱ�ӳ߶ȼĴ���PRES | 8 | 101 | ��д | �Ĵ���ʱ�ӳ߶����ӣ���ʱ���źţ�eclk��ʵ��ָ��������Ƶ���õ�SCL��SDA�������״̬�ת�Ƶ�ͬ��ʱ��ʹ���źţ�eclk-en�� |

������VHDL��I2C���߿��ƺ���ơ��������

- › ����VHDL �ľ�����̼���ʾ��·���

- › ����VHDL�Ŀɱ��ٲʵƿ����������

- › ����VHDL��ͼ����TCDl206���������

- › ����VHDL��99Сʱ��ʱ����Ƽ�ʵ��

- › ����VHDL���Եİ���������·��Ƽ�����

- › ����VHDL��I2C���߿��ƺ����

- �ڰٶ�������������£�����VHDL��I2C���߿��ƺ����

- �ڹȸ�������������£�����VHDL��I2C���߿��ƺ����

- ��soso������������£�����VHDL��I2C���߿��ƺ����

- ���ѹ�������������£�����VHDL��I2C���߿��ƺ����

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

��ǰλ�ã�

��ǰλ�ã�